## Masterarbeit

# **Evaluation and Implementation of Time-Synchronization for Distributed Systems**

# Martin Kammerhofer

\_\_\_\_\_

Institut für Technische Informatik

Technische Universität Graz

Vorstand: O. Univ.-Prof. Dipl.-Ing. Dr. techn. Reinhold Weiß

Begutachter: Univ.-Prof. Dipl.-Ing. Dr. techn. Bernhard Rinner Betreuer: Dipl.-Ing. Dr. techn. Allan Tengg

Graz, im Oktober 2009

#### **Abstract**

Time synchronization of geographically dispersed clocks is a classical problem. An important application is synchronization of distributed computer systems. The problem has been extensively studied for the last 30 years and a large number of algorithms and protocols has been proposed.

This text structures the problem by decomposing it into three partial problems: Precise measurement of the difference between the readings of remote clocks and a local clock, estimation and extrapolation of inner states of the involved clocks, and continuous or periodic adjustment of the local clock to improve future synchronization. Approaches to these partial problems from metrology, mathematics/statistics, and control theory are outlined in a theoretical part and their use in synchronization protocols is described.

The practical part discusses design and implementation of a time synchronization service for the I-SENSE project. I-SENSE is an intelligent multi-sensor multi-level data-fusion framework for distributed embedded systems. Synchronized clocks are mainly required for temporal ordering of video frames from two or more cameras. An evaluation of the implementation on Pentium M and TMS320C64X processors is presented and potential further improvements are discussed.

## Kurzfassung

Die Synchronisation von geographisch verteilten Uhren ist ein klassisches Problem. Eine wichtige Anwendung ist die Synchronisation von verteilten Computersystemen. Zu diesem Problem gibt es sehr umfangreiche Literatur aus den letzten 30 Jahren in der zahlreiche Algorithmen und Protokolle beschrieben werden.

In dieser Masterarbeit wird das Problem auf die folgenden drei Teilprobleme zurückgeführt: Präziser Vergleich des Uhrenstandes einer lokalen Uhr mit entfernten Uhren, Abschätzung und Extrapolation der Zustandsvariablen der beteiligten Uhren und Verbesserung der Synchronisation durch Regelung der lokalen Uhr. Lösungsansätze zu diesen Teilproblemen kommen aus den Disziplinen Metrologie, Mathematik/Statistik und Regelungstechnik. Sie werden im Grundlagen-Teil zusammengefasst dargestellt und ihre Anwendung in Synchronisations-Protokollen wird gezeigt.

Im praktischen Teil wurde für das I-SENSE Projekt ein Zeitsynchronisationsdienst entworfen und implementiert. I-SENSE ist ein intelligentes Multi-Sensor Fusion Framework für verteilte eingebettete Systeme. Synchronisierte Uhren werden hauptsächlich für das zeitlich korrekte Kombinieren von Einzelbildern verschiedener Videokameras benötigt. Eine Beschreibung und Evaluation der Implementierung auf Pentium M und TMS320C64X Prozessoren wird präsentiert und potentielle weitere Verbesserungen werden diskutiert.

|                       | I have explicitly marked   | ntly, that I have not used other than the declare all material which has been quoted either literal        |  |

|-----------------------|----------------------------|------------------------------------------------------------------------------------------------------------|--|

| Eidesstattliche Erklä | ärung                      |                                                                                                            |  |

|                       | nittel nicht benutzt und d | le Arbeit selbstständig verfasst, andere als d<br>lie den benutzten Quellen wörtlich und inhaltlic<br>abe. |  |

| Ort                   |                            | Unterschrift                                                                                               |  |

**Statutory Declaration**

# **Danksagung**

Diese Masterarbeit wurde im Jahr 2008 am Institut für Technische Informatik an der Technischen Universität Graz durchgeführt.

Zu Beginn möchte ich mich bei meinem Betreuer Allan Tengg für seine tatkräftige und kontinuierliche Unterstützung und die konstruktive Zusammenarbeit bedanken. Weiters danke ich meinem Begutachter Herrn Prof. Dr. Bernhard Rinner für seine präzisen Verbesserungsvorschläge und seine Geduld.

An dieser Stelle auch ein herzliches Dankeschön an meine Eltern, deren Verdienste aufzuzählen den Rahmen dieser Seite bei weitem sprengen würde. Ganz besonderer Dank gebührt meiner Partnerin Susanne für den Rückhalt den sie mir gegeben hat und für alles was sie mir abgenommen hat bzw. worauf sie verzichten musste, wenn ich an der Tastatur saß.

Ich widme diese Masterarbeit unserer Tochter Nika, die im Zeitraum des Verfassens geboren wurde.

Graz, im Oktober 2009

Martin Kammerhofer

# FINAL

FOR PUBLIC RELEASE

# **Contents**

| 1. | Intro | duction  | 1                                                           | 1  |

|----|-------|----------|-------------------------------------------------------------|----|

|    | 1.1.  | Motiva   | tion                                                        | 1  |

|    | 1.2.  | Objecti  | ive                                                         | 2  |

|    | 1.3.  | Thesis   | Outline                                                     | 4  |

| 2. | Back  | ground   | l and Terminology                                           | 5  |

|    | 2.1.  | Time, 0  | Clocks and Timescales                                       | 5  |

|    |       | 2.1.1.   | Properties of time                                          | 5  |

|    |       | 2.1.2.   | Relativistic effects                                        | 5  |

|    |       | 2.1.3.   | The second                                                  | 5  |

|    |       | 2.1.4.   | Timescales                                                  | 6  |

|    | 2.2.  | Charac   | terization of Clocks                                        | 9  |

|    |       | 2.2.1.   | Mathematical models of oscillators and clocks               | 9  |

|    |       | 2.2.2.   | Accuracy, precision, resolution, and stability              | 12 |

|    | 2.3.  | Hardw    | are Clocks                                                  | 14 |

|    |       | 2.3.1.   | Crystal oscillators                                         | 14 |

|    |       | 2.3.2.   | Other frequency sources                                     | 16 |

|    |       | 2.3.3.   | Computer clocks                                             | 17 |

|    |       | 2.3.4.   | External reference clocks                                   | 20 |

|    |       | 2.3.5.   | Interfacing external clocks                                 | 21 |

|    | 2.4.  | Softwa   | re Clocks                                                   | 21 |

|    |       | 2.4.1.   | Operating system view                                       | 21 |

|    |       | 2.4.2.   | Clock phase and rate adjustment                             | 22 |

|    |       | 2.4.3.   |                                                             | 23 |

|    | 2.5.  | Genera   |                                                             | 24 |

|    |       | 2.5.1.   |                                                             | 25 |

|    |       | 2.5.2.   |                                                             | 27 |

|    |       | 2.5.3.   | Adjusting the local clock to reduce future time differences | 29 |

| 3. | Sync  | chroniza | ation Protocols for Computer Networks                       | 30 |

|    | 3.1.  | Classif  | ication of Synchronization Protocols                        | 30 |

|    |       | 3.1.1.   | Communication model                                         | 30 |

|    |       | 3.1.2.   |                                                             | 31 |

|    |       | 3.1.3.   | Clock correction versus timescale transformation            | 31 |

|    |       | 3.1.4.   |                                                             | 31 |

|    |       | 3.1.5.   |                                                             | 32 |

|    |       | 316      |                                                             | 37 |

|     |                 | 3.1.7.   | Lifetime and scope                                            | 32              |  |

|-----|-----------------|----------|---------------------------------------------------------------|-----------------|--|

|     |                 | 3.1.8.   | Low level access                                              | 32              |  |

|     | 3.2.            | Synchro  | onization Protocol Survey                                     | 33              |  |

|     |                 | 3.2.1.   | Logical clocks                                                | 33              |  |

|     |                 | 3.2.2.   | Cristian's algorithm                                          | 35              |  |

|     |                 | 3.2.3.   | The Berkeley algorithm                                        | 36              |  |

|     |                 | 3.2.4.   | Marzullo's algorithm                                          | 36              |  |

|     |                 | 3.2.5.   | Fault tolerant protocols                                      | 37              |  |

|     |                 | 3.2.6.   | Protocols for wireless sensor networks                        | 37              |  |

|     | 3.3.            | The Ne   | twork Time Protocol                                           | 38              |  |

|     |                 | 3.3.1.   | NTP classification                                            | 38              |  |

|     |                 | 3.3.2.   | History and background                                        | 39              |  |

|     |                 | 3.3.3.   | NTP implementations                                           | 40              |  |

|     |                 | 3.3.4.   | NTP sub-algorithms                                            | 40              |  |

|     |                 | 3.3.5.   | The Simple Network Time Protocol                              | 46              |  |

|     | <b>T:</b> -     | 0        | vanisation for the LOCNOC Everyousely                         | 47              |  |

| 4.  |                 |          | ronization for the I-SENSE Framework SE Architecture Overview | <b>47</b><br>47 |  |

|     | 4.1.            | 4.1.1.   | Hardware architecture                                         | 47              |  |

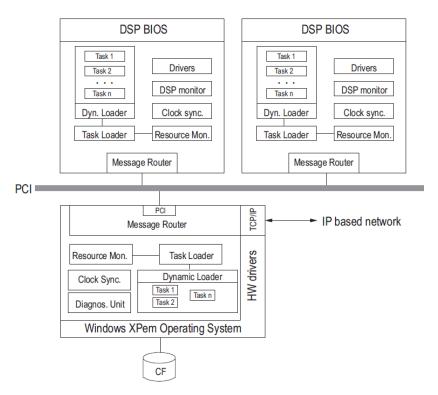

|     |                 | 4.1.1.   | Software architecture                                         | 48              |  |

|     |                 | 4.1.2.   | The I-SENSE message subsystem                                 | 49              |  |

|     | 4.2.            |          | Decisions and Their Rationale                                 | 51              |  |

|     | 4.2.            | 4.2.1.   | Choice of transport layer                                     | 51              |  |

|     |                 | 4.2.2.   | Choice of implementation layer                                | 52              |  |

|     |                 | 4.2.3.   | Inter-node protocol and implementation selection              | 52              |  |

|     |                 | 4.2.4.   | Intra-node protocol and implementation                        | 52              |  |

|     | 4.3.            |          | onfiguration                                                  | 53              |  |

|     |                 |          | Intra-node Synchronization Protocol                           | 54              |  |

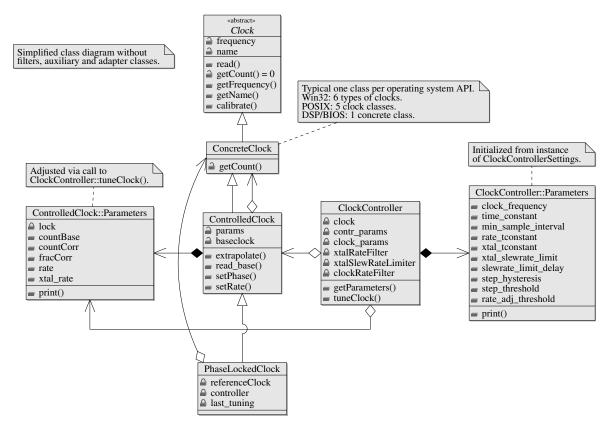

|     | т.т.            | 4.4.1.   | Implementation classes overview                               | 54              |  |

|     |                 | 4.4.2.   | Timestamp format and timescales                               | 57              |  |

|     |                 | 4.4.3.   | The custom algorithm                                          | 58              |  |

|     |                 | т.т.Э.   | The custom argorithm                                          | 50              |  |

| 5.  | Evalu           | uation   |                                                               | 61              |  |

|     | 5.1.            | Inter-no | ode Evaluation                                                | 61              |  |

|     | 5.2.            | Intra-no | ode Evaluation                                                | 63              |  |

|     | 5.3.            | End-to-  | end Evaluation                                                | 65              |  |

| _   | •               |          |                                                               |                 |  |

| ь.  |                 | clusion  | Work                                                          | <b>69</b>       |  |

|     | 0.1.            | ruture   | WOIK                                                          | 69              |  |

| A.  | List            | of Symb  | pols                                                          | 71              |  |

| В.  | Abbr            | eviation | ns and Glossary                                               | 73              |  |

| Bik | Bibliography 78 |          |                                                               |                 |  |

# **List of Figures**

| 1.1.  | I-SENSE node hardware architecture                                 | 3  |

|-------|--------------------------------------------------------------------|----|

| 1.2.  | A simple fusion model                                              | 3  |

| 1.3.  | Diurnal frequency variation of a computer clock                    | 4  |

| 2.1.  | Oscillator + Counter = Clock                                       | 9  |

| 2.2.  | Accuracy, Precision, and Stability                                 | 12 |

| 2.3.  | Graphical explanation of MTIE                                      | 14 |

| 2.4.  | Frequency-Temperature vs. Angle-of-Cut for AT-cut crystal          | 15 |

| 2.5.  | Short term stability ranges of various frequency standards         | 18 |

| 2.6.  | Frequency variation of a computer clock over a week                | 20 |

| 2.7.  | Clock adjustment sawtooth error                                    | 22 |

| 2.8.  | Two-way time transfer                                              | 25 |

| 2.9.  | Common-view method                                                 | 26 |

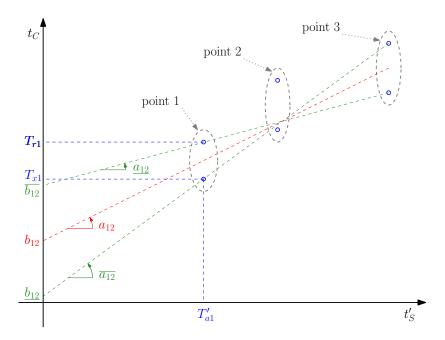

| 2.10. | . Offset and skew estimation in the Tiny-Sync protocol             | 28 |

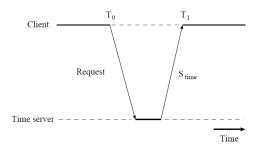

| 3.1.  | Cristian's remote clock reading method                             | 35 |

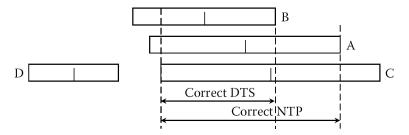

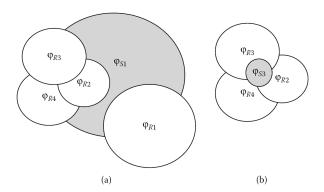

| 3.2.  | Marzullo's interval intersections                                  | 37 |

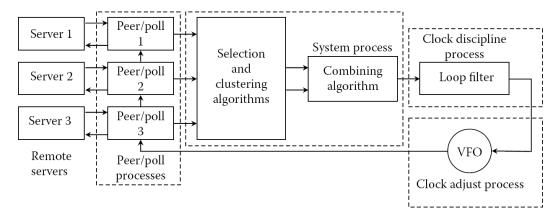

| 3.3.  | NTP architecture overview                                          | 41 |

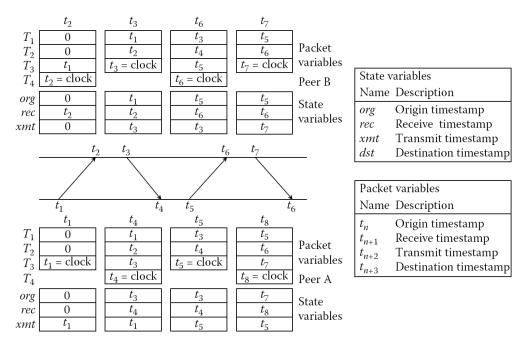

| 3.4.  | NTP timestamp exchange                                             | 42 |

| 3.5.  | NTP clustering algorithm example                                   | 43 |

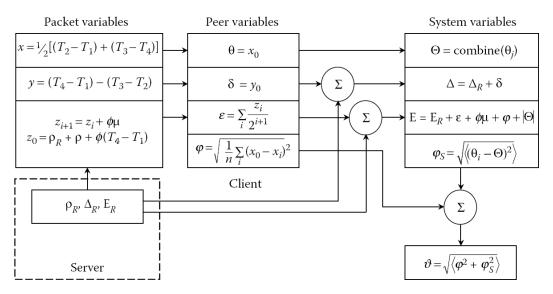

| 3.6.  | NTP error budget calculations                                      | 44 |

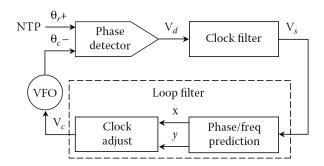

| 3.7.  | NTP clock discipline algorithm                                     | 45 |

| 4.1.  | I-SENSE node                                                       | 48 |

| 4.2.  | I-SENSE middleware services                                        | 49 |

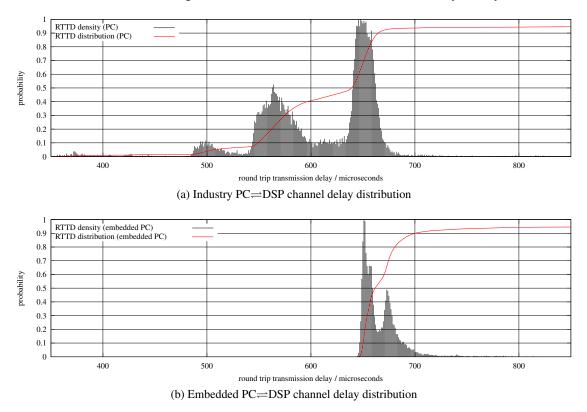

| 4.3.  | DSP $\rightarrow$ x86 $\rightarrow$ DSP round trip time histograms | 50 |

| 4.4.  | Additional I-SENSE framework classes                               | 54 |

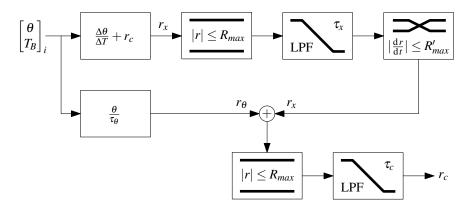

| 4.5.  | Clock controller implementation                                    | 56 |

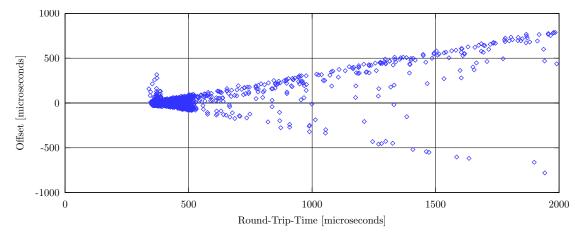

| 4.6.  | Offset versus round-trip time scatter diagram                      | 58 |

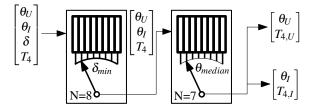

| 4.7.  | Clock filter implementation                                        | 58 |

| 4.8.  | Client (TMS320C64X) synchronization loop                           | 60 |

| 4.9.  | Server (Pentium M) synchronization loop                            | 60 |

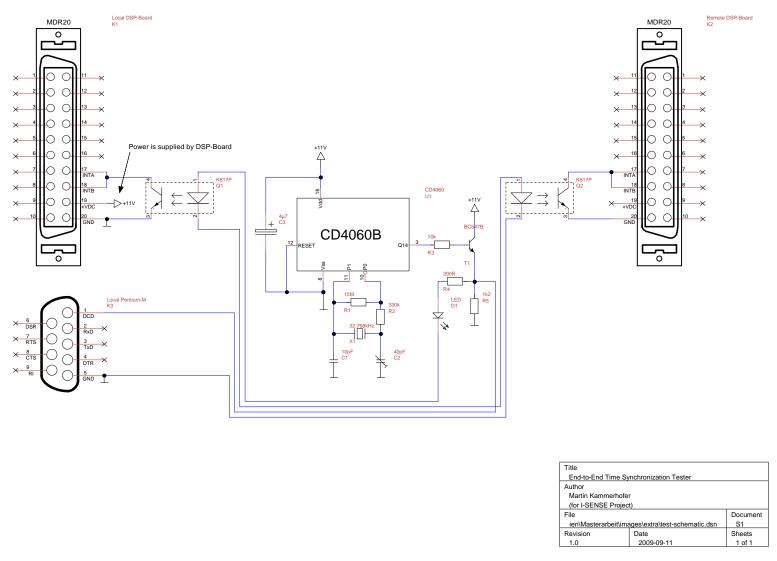

| 5.1.  | Schematic circuit diagram of external test hardware                | 66 |

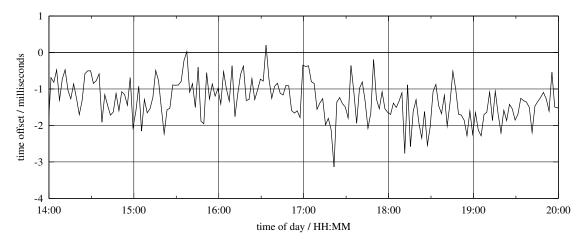

| 5.2.  | Client clock with spurious 1 ms steps                              | 67 |

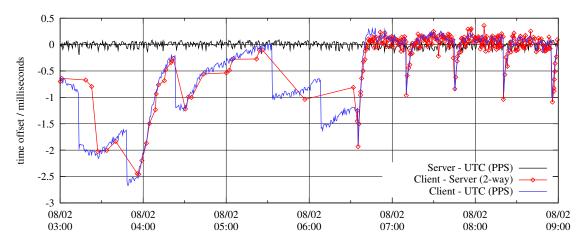

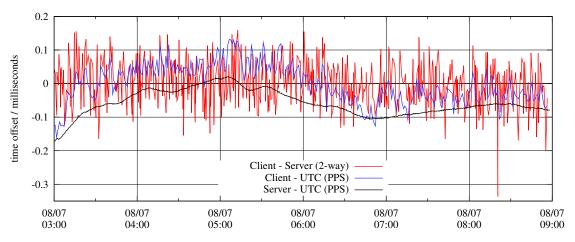

| 5.3.  | NTP with stratum 1 server on same LAN                              | 67 |

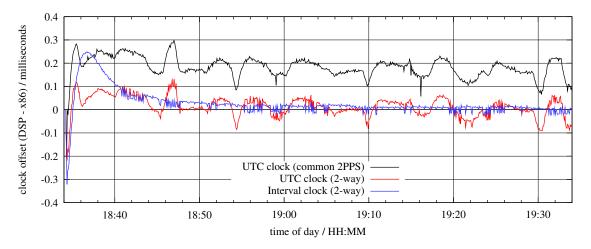

| 5.4.  | Clock differences between x86 CPU and DSP                          | 67 |

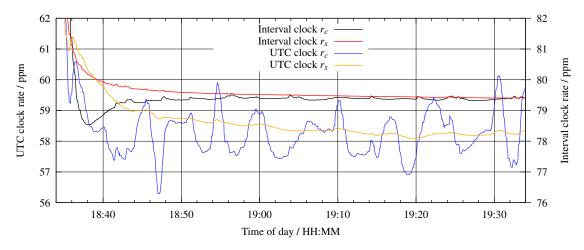

| 5.5.  | Clock rates                                                        | 68 |

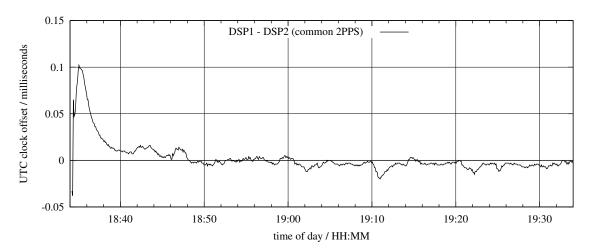

| 5.6.  | Clock difference between two local DSPs                            | 68 |

| 5.7.  |                                                                    |    |

# **List of Tables**

| 2.1. | Positive leap second                                 | 8  |

|------|------------------------------------------------------|----|

| 2.2. | Temporal orderings of ambiguous timestamps           | 9  |

| 2.3. | Frequency control device market (Estimates for 2006) | 15 |

| 2.4. | Resynchronization and recalibration intervals        | 17 |

| 2.5. | Time representations in various APIs                 | 23 |

| 2.6. | Epochs of some computer timescales                   | 24 |

| 2.7. | Message delivery processing steps                    | 27 |

| 4.1. | I-SENSE inter-node communication channel delay       | 51 |

| 4.2. | Inter-node synchronization message format            | 59 |

| 5.1. | Clock controller parameters                          | 64 |

## 1. Introduction

Most distributed tasks require some sort of synchronization. A straightforward and intuitive way of supplying synchronization is *time synchronization*. Synchronized clocks have many uses in distributed systems. They simplify many distributed algorithms and improve their performance [Lis93].

Although time synchronization is a classical problem, there is no *general* solution. The literature on the subject is vast—there are thousands of publications and research is still ongoing.<sup>1</sup>

Among the reasons for the abundance in literature and protocols are the strong dependency of time synchronization implementations on specific properties of the hardware and software environment, and the tremendously varying demands of individual applications. The focus on a specific use case—time synchronization for the I-SENSE middleware—will therefore narrow down the broad path that is implied by the title of this thesis.

This chapter will motivate why the I-SENSE framework needs a time synchronization implementation in section 1.1, set the goals for this thesis in section 1.2, and sketch the structure of this text in section 1.3.

#### 1.1. Motivation

The major goal of the I-SENSE research project<sup>2</sup> is a scalable and embedded architecture for various multi-sensor applications [KRT06, TKR07, KTR08]. The project combines the scientific research areas *multi-sensor data fusion* and pervasive embedded computing. The main idea is to provide a generic architecture, which supports distributed realtime multi-level data fusion on an embedded system.

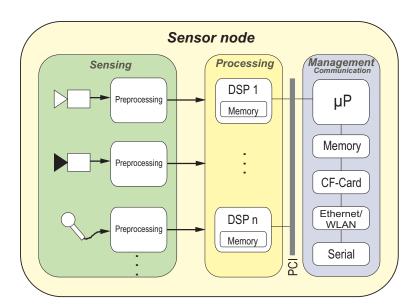

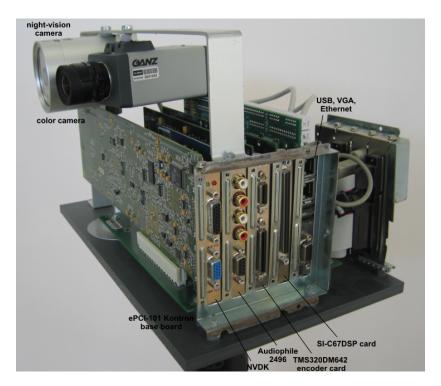

The architecture of an I-SENSE sensor node is depicted in fig. 1.1 and a photo is shown in fig. 4.1 on page 48.

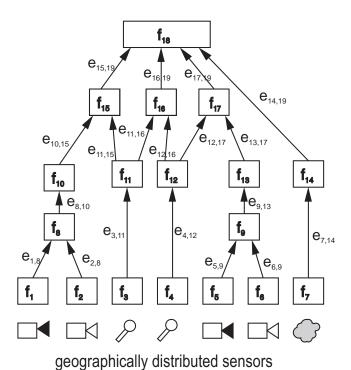

Distributed fusion applications are described by a *fusion model*. The fusion model can be represented as a weighted directed acyclic task graph. An example is shown in fig. 1.2. Several fusion tasks  $f_i$  process data from different sensors. Synchronized timestamps are a prerequisite for this multi-sensor data fusion.<sup>3</sup>

A March 2009 CiteSeer query for "time synchronization" brought up 3046 results. A Google Scholar query for "synchronization protocol" yielded 6190 articles. A significant part of the third millennium research is in the context of (wireless) sensor networks.

$<sup>^2</sup>$  http://www.iti.tugraz.at/en/research/isense/index.html

More exactly, while multi-sensor data fusion without time synchronization is doable, it requires more complex correlation algorithms, more CPU and memory resources, and is therefore avoided.

As a case study for the I-SENSE approach, a traffic surveillance system has been developed. Video cameras, microphones and light barriers are deployed as sensors. Sensor fusion is used to achieve vehicle detection, tracking and classification. Video stream fusion requires temporal alignment at the frame level. If any two clocks that generate frame timestamps differ by an offset less than

offset

$$< \frac{1}{2* \text{highest frame rate}}$$

(1.1)

then matching of frames can be done in straightforward ways. <sup>4</sup>[DFH<sup>+</sup>08] With practical video frame rates, equation 1.1 translates to a requirement of a few milliseconds for the upper clock error bound.

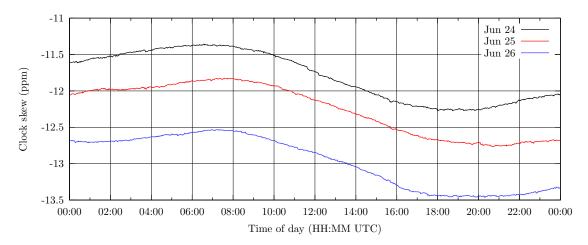

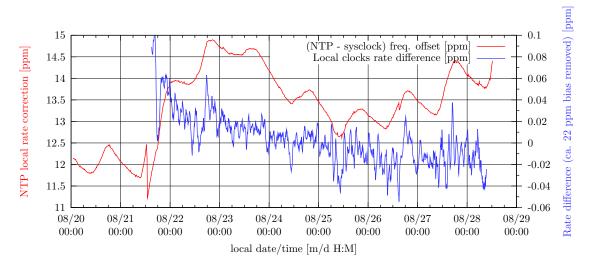

An ideal clock would proceed at a rate of 1 second per second of standard time. Practical clocks are imperfect and deviate from this ideal rate. Crystal oscillator based computer clocks show manufacturing dependent frequency tolerances, frequency deviations that depend on temperature, and frequency aging effects. Unattended computer clocks therefore drift apart. Fig. 1.3 shows the clock skew of a computer clock. The depicted clock is rather good.<sup>5</sup> Frequency errors of a few hundred ppm are not uncommon in cheap crystals oscillators for computer clocks [MD08]. Moreover, temperature dependent clock rate variations can be expected to be much larger in outdoor deployed embedded systems. A constant clock skew of only 1 ppm accumulates a clock offset error of 86,4 ms over a day.

Time synchronization for the I-SENSE framework—although planned from the beginning of the project—was still unimplemented prior to this thesis. Only an intra-node pre-synchronization feature was available, i. e., the clocks of all processors within a sensor node (cf. fig. 1.1) were synchronized during middleware startup, and pre-configured static rate corrections were applied. This was sufficient for development and testing, but would not have worked over extended periods of time.

### 1.2. Objective

The goal of this thesis is to extend the functionality of the I-SENSE framework with a mechanism for time synchronization. This extension must perform adequately, to allow fusion of two real time video streams originating from different sensor nodes. The following subgoals are defined:

- 1. Investigation of existing procedures for time synchronization in distributed systems

- 2. Selection of a suitable mechanism or protocol

- 3. Implementation of the chosen solution on the Windows XP embedded (Pentium-M) and DSP/BIOS (TMS320C64X) platforms

- 4. Evaluation of the implementation

To have some margin for higher frame rates, the aim for maximum clock offset error is 5 ms.<sup>6</sup>

<sup>&</sup>lt;sup>4</sup> This assumes that creation of timestamps is perfect, i. e., reading the clocks does not introduce additional time offset errors.

<sup>&</sup>lt;sup>5</sup> The machine is fitipc150, a commodity PC located in the ITI VLSI laboratory, which happened to be the main development machine for the practical part of this thesis.

<sup>&</sup>lt;sup>6</sup> The 5 ms value follows from an assumed maximal frame rate of 100 Hz inserted into equation 1.1. The current traffic surveillance use case performs well with frame rates of only 15...30 Hz.

1.2. Objective

Figure 1.1.: I-SENSE node hardware architecture

Figure 1.2.: A simple fusion model [TKR07]

Figure 1.3.: Diurnal frequency variation of a computer clock over three consecutive days

#### 1.3. Thesis Outline

Chapter 2 gives a thorough introduction into the problem of time synchronization. Important concepts like timescales, clocks, measurement of remote clocks, and synchronization methods are explained. Most of the chapter treats synchronization from a high level perspective, but details pertaining to commonly used operating systems and current PC hardware are given too.

Chapter 3 explores the huge subject of synchronization protocols for distributed computer systems. First a discussion of several important classification criteria explains, why the design space for protocols is so large. The following protocol survey presents some key concepts of important contributions to the field. For reasons of space, only the NTP and SNTP protocols are described in detail, but references to important papers and survey literature are given.

Chapter 4 first describes aspects of the I-SENSE platform, which are relevant for time synchronization implementation. The high level structure of the implementation is then explained with reference to four important design decisions. Several object oriented clock abstractions are presented next, on which the implementation is built. An implementation overview concludes the chapter.

Evaluation was somewhat constricted by lack of resources.<sup>7</sup> However several experiments have been conducted, which yielded very satisfying results. The setup and methodology of these experiments is presented together with graphical results in chapter 5.

Chapter 6 concludes the thesis with a summary and suggestions for future work.

<sup>7</sup> Hardware timestamping facilities and embedded I-SENSE nodes.

# 2. Background and Terminology

#### 2.1. Time, Clocks and Timescales

#### 2.1.1. Properties of time

Time is the physical quantity that can be measured with the highest accuracy; yet still there is no satisfactory answer to the (philosophical and scientific) question "What is time?" [Sch94b]. We cannot study the flow of time under a microscope, impede it or experiment with it. We do not know what exactly happens when time passes. Important for our purposes are, that

- time differences can be measured with clocks, and

- time defines the (temporal) order of events.

#### 2.1.2. Relativistic effects

Time is neither absolute nor independent from space. According to the theory of special relativity it is possible, that different observers, even after correcting for propagation delays, find different orderings for the same set of events.<sup>1</sup> Time dilatation depends on the ratio of the relative speed between clocks v to the speed of light c as  $[1-(v/c)^2]^{-1/2}$  (Lorentz factor). A consequence of general relativity is, that time flows slower in higher gravitational fields. Gravitational time dilatation makes a clock gain 9.4 ns per day, when lifted up 1 km from sea level.<sup>2</sup>

The magnitudes of relativistic effects are very small at everyday live speeds ( $v \ll c$ ) and locations near the earth surface. The timing uncertainty of computer clocks is several orders of magnitude larger than these effects. Newtonian space-time is therefore assumed for the rest of this thesis.

#### 2.1.3. The second

Time interval is one of seven base quantities of the International System of Units (SI) [BIP06]. The unit of time interval is the second.

Historically the second has been defined as the fraction 1/86400 of the mean solar day. Because the spin rate of the earth is irregular on short time scales and decreasing on long time scales,<sup>3</sup> from

<sup>&</sup>lt;sup>1</sup> This is known as relativity of simultaneity.

<sup>&</sup>lt;sup>2</sup> At latitude  $40^{\circ}$  the clock increases its rate by  $1.091 \times 10^{-16} \,\mathrm{m}^{-1}$  [Vig07, p. 8-22].

<sup>&</sup>lt;sup>3</sup> The long-term average rate of increase in the length of the day is about 1.7 ms per century. Immanuel Kant suggested as early as 1754 a steady deceleration of earth rotation due to tidal friction [NMM<sup>+</sup>01].

1960 to 1967 the SI second was defined as a certain fraction of the tropical year 1900 (ephemeris second). Since 1967 the definition of the second is completely decoupled from astrometry. The current definition of the SI second is derived from an atomic resonance of the <sup>133</sup>Cs (caesium) atom:<sup>4</sup>

The second is the duration of 9 192 631 770 periods of the radiation corresponding to the transition between the two hyperfine levels of the ground state of the caesium 133 atom.

This definition refers to a caesium atom at rest at a temperature of zero Kelvin [BIP06].

Today a small number of national metrology laboratories realize the unit of time through primary frequency standards. The best of these primary standards produce the SI second with a relative standard uncertainty of some parts in 10<sup>16</sup> [BIP07].

#### 2.1.4. Timescales

Clocks only count intervals. To agree on *dates*, timescales are needed. A *timescale* is a system of assigning labels (dates) to *time instants* (events). (The ISO 8601 standard specifies numeric representations of date and time.) The origin (reference date) of a timescale is called the *epoch*. A (global) timescale should have the following properties [Ari05]:

**Reliability** Clocks have a large MTBF. The timescale tolerates failure of clocks, i.e., there are redundant clocks.

**Frequency stability** The unit of scale is constant. Two time scale readings determine the length of a time interval.

**Frequency accuracy** The unit of scale is as close as possible to its definition.

**Accessibility** The timescale is universally accepted. It provides a way to date events for everyone.

Time is an immaterial quantity. Measurement of time is based on physical phenomena that depend on time. There are two ways to get a timescale from a physical phenomenon.

**Dynamic timescale** A dynamical physical system is observed. The system has a mathematical model in which time is the independent parameter. The model allows, given an observed state of the system, to determine unambiguously the time of the observation. Particular states of the system (events) serve as labels on the timescale. The unit of time is conveniently defined e. g., as a time constant of the mathematical model or the interval between observable periodic events. The *Universal Time* family of timescales (UT0, UT1, UT1R, UT2 and UT2R) are dynamic.

**Integrative timescale** The unit of time is a time interval defined by a reproducible physical phenomenon. The timescale continuously accumulates (counts) the units of time. Other than a well defined unit, a integrative timescale needs a convention about a fixed origin. All atomic timescales are integrative.

When better frequency standards than caesium atomic clocks become widely available, the definition of the second will certainly change again.

<sup>&</sup>lt;sup>5</sup> A realization of an integrative timescale accumulates errors in the realization of the unit too.

Today global timescales are realized through international cooperation. In 1912 the Bureau International de l'Heure (BIH) was founded. Its responsibility for combining different time measurements was taken over by the Bureau International des Poids et Mesures (BIPM) in 1987.

#### International atomic time (TAI)

National laboratories usually operate a number of atomic clocks. These clocks run independently. Based on the results of local comparisons between these clocks a combined laboratory timescale is created. The combined timescale is (usually) more accurate and stable than any of the contributing clocks. These timescales are designated TA(k) for laboratory k.

The BIPM uses comparisons between some 300 atomic clocks in about 60 national time laboratories to form International Atomic Time (TAI). The details of the algorithms used to compute TAI are quite complex and have been changed several times in the past [GA05].

Methods of comparison of distant clocks are a prime requisite to calculate TAI. Frequency and time transfers are made with GPS and by two-way satellite links. The uncertainty of clock comparison is today between a few tens of nanoseconds and a nanosecond for the best links [GA05].

TAI is a "paper clock" not available in real time. TAI and UTC are disseminated every month by Circular T, a monthly publication of the BIPM.

Version 4 of the Network Time Protocol (NTPv4) can be configured to disseminate the TAI – UTC offset in addition to UTC [LM00].

#### Universal time (UT)

Universal time (UT1) is based on the rotation angle of the earth on its axis relative to the mean sun. It is popularly, but erroneously, known as Greenwich Mean Time (GMT). The rotation of the Earth and UT1 are now monitored by the International Earth Rotation Service (IERS).<sup>6</sup> Modern techniques like *Very Large Baseline Interferometry* (VLBI) allow the determination of UT1 with an uncertainty of 10 µs [GA05].

UT1 has applications in astronomy, geodesy, space navigation and satellite tracking; but it is nowadays of little importance for the general public.

#### Coordinated universal time (UTC)

UTC is today the basis for almost all official national timescales and therefore widely available. Since 1 January 1972 00:00:00 UTC the present system is in use. The UTC second ticks synchronously with the TAI second. Leap seconds are infrequently added to the UTC timescale to keep the absolute value of dUT1 = UT1 - UTC below  $0.9 \, s.^7 \, UTC - TAI$  is -34 s at the time of this writing. Scheduled

<sup>&</sup>lt;sup>6</sup> Knowing the universal time of a sextant sighting was historically very important for determining the longitude. A timing error of 1 s leads to an error in longitude of 15 arc-seconds, i. e., 463 m on the equator.

<sup>&</sup>lt;sup>7</sup> In theory leap seconds can also be removed from the UTC timescale. This has never happened, and—according to present knowledge about earth rotation—it is unlikely that it will ever happen.

| Date             | UTC Time    | UTC – TAI [s] | POSIX time [s] | dUT1 [s]  |

|------------------|-------------|---------------|----------------|-----------|

| 2008 December 31 | 23h 59m 59s | -33           | 1230767999     | -0.592841 |

| 2008 December 31 | 23h 59m 60s | -33           | 1230768000     | -0.592841 |

| 2009 January 1   | 0h 0m 0s    | -34           | 1230768000     | 0.407159  |

Table 2.1.: Positive leap second

insertions of leap seconds are announced several months before the fact through the biannual IERS "Bulletin C".

Insertion of a 61<sup>st</sup> second into the last minute of the year 2008 is shown in table 2.1. Removal of a second from UTC, i. e., a minute with only 59 seconds, is very unlikely to ever happen.

Because of the problems associated with leap seconds, a new definition of UTC is being discussed. [NMM<sup>+</sup>01] Several international scientific organizations are currently evaluating the subject. The U. S. submitted a proposition to abandon leap seconds (and replace them with leap hours) to the ITU-R in 2004. No decision will will be made before 2011.

#### Representation of UTC in POSIX and Windows

Most operating systems cannot fully cope with leap seconds. Operating systems represent timestamps internally as an integer count of (a constant fraction of) seconds. Structured representations—seconds, minutes, hours and so on—are used only for input and output and are conveniently interpreted with reference to the local time zone, with or without daylight saving time. Two assumptions are built in:<sup>8</sup>

- 1. Timestamps are to be interpreted as the number of seconds between the specified time and the epoch.

- 2. Each day (since the epoch) has a duration of exactly 86400 seconds.

These assumptions about the timescale contradict the definition of UTC.

The rationale for assumption 2 is to keep algorithmic conversions between the internal scalar representation and the broken down representation simple. Otherwise, a faithful implementation of the conversions would incur the overhead of consulting a leap second table.

It is impossible to implement a uniform and continuous UTC timescale based on the above assumptions. Operating systems with UTC clocks have to handle leap seconds somehow. Some options for positive leap second handling are:

- 1. ignore leap seconds

- 2. jump back 1 s at the beginning of the leap second

- 3. jump back 1 s at the end of the leap second

<sup>8</sup> Specified e. g., in POSIX.1/IEEE 1003.1-1996 and handled the same way in Microsoft Windows operating systems.

| $t_A$ [s] | $t_B$ [s] | $ t_A - t_B $ [s] |

|-----------|-----------|-------------------|

| L + 0.5   | L + 0.6   | 0.1               |

| L + 0.5   | L + 1.6   | 1.1               |

| L + 1.5   | L + 0.6   | 0.9               |

| L + 1.5   | L + 1.6   | 0.1               |

Table 2.2.: Temporal orderings of ambiguous timestamps

Figure 2.1.: Oscillator + Counter = Clock

- 4. stop the clock during the leap second

- 5. reduce the clock frequency in an interval around the leap second to gradually loose one second.<sup>9</sup>

POSIX as well as Windows use method 1 if no time service is configured, i. e., they loose synchronization to UTC after the leap second. Method 3 is used when operating as an (S)NTP client and/or server. Stepping back the clock violates the fundamental assumption of monotonic increasing time. Clock steps introduce discontinuities to the timescale. A leap second inserted at time L causes ambiguous timestamp during the interval [L, L+2]. As an example consider two sensor events A and B with scalar timestamps L+0.5 s and L+0.6 s, respectively. Table 2.2 lists the possible temporal orderings. In general relative errors in measured intervals are unbounded and sign inversions can happen!

#### 2.2. Characterization of Clocks

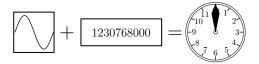

Any time measurement device must somehow realize the second. Practical clocks use an oscillating device, to determine (a constant fraction of) the second, and a counter to accumulate these time intervals (cf. fig 2.1). The vast majority of computer clocks uses crystal oscillators. Embedded systems use ceramic resonators and RC-oscillators too.

#### 2.2.1. Mathematical models of oscillators and clocks

The instantaneous output voltage v(t) of an oscillator is

$$v(t) = [V_0 + \Delta V(t)] \cos[2\pi v_0 t + \varphi(t)]$$

(2.1)

This was proposed as UTC-SLS (UTC with Smoothed Leap Seconds).

<sup>&</sup>lt;sup>10</sup> Provided the machine in question was previously synchronized by other means, e.g., with a one-shot clock adjustment program like the ntpdate utility.

<sup>&</sup>lt;sup>11</sup> It breaks Lamport's *Happened-Before* relation described in section 3.2.1 on page 33.

<sup>&</sup>lt;sup>12</sup> Other types of clocks exist, but play no practical role in time measurement.

where constants  $V_0$  and  $v_0$  represent nominal amplitude and frequency, respectively. Amplitude fluctuations can be converted to phase fluctuations, but quality oscillators usually have small fractional amplitude fluctuations that are neglected.

$$\frac{\Delta V(t)}{V_0} \ll 1$$

and therefore  $\Delta V(t) \equiv 0$  is assumed (2.2)

The instantaneous frequency v(t) is the derivative of the phase.

$$v(t) = v_0 + \frac{1}{2\pi} \frac{\mathrm{d}\varphi(t)}{\mathrm{d}t} \tag{2.3}$$

The dimensionless instantaneous fractional frequency deviation y(t) is defined as

$$y(t) = \frac{\Delta f}{f} = \frac{v(t) - v_0}{v_0} = \frac{1}{2\pi v_0} \frac{d\varphi(t)}{dt} = \frac{dx(t)}{dt}$$

(2.4)

Measuring instantaneous frequency is impossible, because it would require measurement equipment with infinite bandwidth. Frequency measurement *always* involves *two* oscillators and some sampling/averaging time  $\tau$ .<sup>13</sup> In practice fractional frequency deviation is averaged as

$$\bar{y}(t) = \frac{x(t+\tau) - x(t)}{\tau} \tag{2.5}$$

When we consider an oscillator as a clock, the fractional phase fluctuation x(t) represents the accumulated *time error* over the interval  $[0, t]^{-14}$

$$x(t) = \int_{0}^{t} y(t') dt' = \frac{\varphi(t)}{2\pi v_0}$$

(2.6)

There are many ways how an oscillator can be interfaced to a counter to build a clock; hence the counter frequency can be different from the oscillator frequency. Analog (PLL) and digital techniques (prescaler, adder) are used for clock rate correction [Loy97, p. 30–34]. Most computer clocks either count whole oscillator cycles (e. g., a PCC) or divide the oscillator frequency by a constant factor with a fixed or programmable prescaler.

Almost all authors model clocks as *continuous* monotonic functions C(t) that map from real time to *clock time*. To make the distinction between real time and clock readings clear, capital letters are used for timestamps.

$$T_i = C(t_i) (2.7)$$

The rate R of a clock is the first derivative of the clock function

$$R(t) = \frac{\mathrm{d}C(t)}{\mathrm{d}t} \tag{2.8}$$

$<sup>^{13}</sup>$  The sampling time au could e. g., be the gate time of a counter.

<sup>&</sup>lt;sup>14</sup> Some authors use x(t) to denote the *random* part of time error only.

<sup>&</sup>lt;sup>15</sup> Also known as *virtual time* or *logical time* in the literature.

A perfect clock would have no rate deviations, i. e.,  $R(t) \equiv 1$ . A clock with R > 1 is called *fast* or *early*, and it is said to *gain* time. A clock with R < 1 is *slow*, *late*, and *looses* time. The rate is modeled as

$$R(t) = 1 + S + Dt + E_i(t) + v(t)$$

(2.9)

where S is the fractional frequency offset or skew, D is the linear fractional frequency drift rate due to aging,  $E_i(t)$  is the frequency dependency on environmental conditions (temperature, etc.) and v(t) is the random rate fluctuation (frequency modulation noise). Linear frequency aging D is a simplification, but higher order terms are hardly ever used.

The most commonly used model to represent clock noise in the frequency domain is the *power-law* noise model. The power spectral density (PSD) of v(t) is modeled as a linear combination [Bre97]

$$S_{y} = \sum_{\alpha = -2}^{2} h_{\alpha} f^{\alpha} \qquad f \le f_{h}$$

(2.10)

where f is the Fourier frequency and the five coefficients  $h_{-2}, \dots, h_2$  are device dependent parameters. The upper cutoff frequency  $f_h$  depends on the low-pass filtering of the oscillator, its output buffer amplifier and the bandwidth of the measurement system.<sup>17</sup> The relation between the PSDs of frequency deviation (2.4) and time error (2.6) is [SAHW90, p. TN-34]

$$S_x = \frac{1}{(2\pi f)^2} S_y = \frac{1}{4\pi^2} \sum_{\alpha = -2}^{2} h_{\alpha} f^{\alpha - 2} \qquad f \le f_h$$

(2.11)

Most oscillator data sheets however show a plot of the SSB phase noise to carrier power ratio <sup>18</sup> in dBc/Hz [Ril03]

$$\mathcal{L}(f) = 10\log\left[\frac{1}{2}S_{\phi}(f)\right] = 10\log\left[\frac{1}{2}(2\pi\nu_0)^2S_x(f)\right]$$

(2.12)

Future clock values can be predicted as

$$C(t_1) = C(t_0) + \int_{t_0}^{t_1} R(t') dt' = T_0 + (1+S)(t_1 - t_0) + \frac{1}{2}D(t_1 - t_0)^2 + \int_{t_0}^{t_1} [E_i(t') + v(t')] dt'$$

(2.13a)

Practical application of equation 2.13a requires a lot of knowledge about the clock in question, its reactions to environmental conditions, and needs careful control and/or monitoring of those conditions. Over short to medium intervals  $\Delta t = (t_1 - t_0)$  and for most clocks, the contributions of clock aging D and noise v(t) to the time error  $(T_1 - T_0 - \Delta t)$  are typically minuscule compared to skew S and temperature sensitivity. A much simpler model of short-time clock prediction is

$$C(t_1) \approx C(t_0) + [1 + S(t_0)](t_1 - t_0)$$

(2.13b)

In contrast to equation 2.13a it is assumed that the rate R(t) has only minor variation over interval  $[t_0, t_1]$ . This is reasonable, provided that  $(t_1 - t_0)$  is small enough, so that environment conditions are stable and aging and noise are insignificant.

<sup>&</sup>lt;sup>16</sup> Unfortunately, the literature uses much inconsistent terminology. Especially the terms skew and drift denote many different concepts.

<sup>&</sup>lt;sup>17</sup> In practice there is also a lower cutoff frequency  $f_l$  due to the finite duration of the measurement.

<sup>&</sup>lt;sup>18</sup> Although  $\mathcal{L}(f)$  is not recommended by the literature.

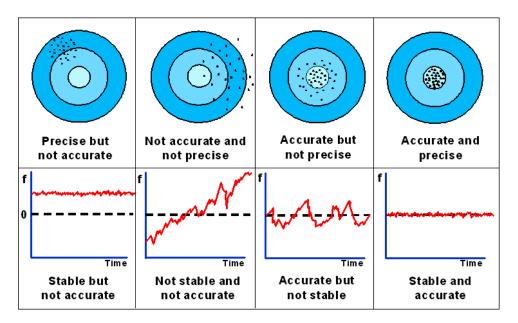

Figure 2.2.: Accuracy, Precision, and Stability [Vig07, p. 4-2]

#### 2.2.2. Accuracy, precision, resolution, and stability

A graphical explanation of the terms accuracy, precision, and stability is depicted in fig. 2.2.

**Accuracy** A measurement is *accurate* if the result is close to the true value of the measurand.

**Precision** Measurements are *precise*, if repeated measurements produce small variation in results. Precision is the degree of specified detail which can be observed. It corresponds to the number of *significant* digits in measurement results, which can be obtained repeatably and reliably. 19

**Resolution** is the granularity of a measurement result, i. e., the minimum (digital) non-zero difference between readings.

**Stability** is the quality of being free from change or variation. Stability is a property of an observed quantity; it is not a property of its measurement.

Calibration can compensate a lack of frequency accuracy (i. e., a frequency offset). Good resolution is accomplished with high counter frequency. Synchronization—setting the clock to the same time as a reference clock—establishes time accuracy. Frequency stability determines, how long a clock can keep the time error within specified bounds. Unstable clocks need much shorter resynchronization/recalibration intervals than more stable clocks (cf. table 2.4).

Various variances and deviations (square roots of variances) are used to characterize the fluctuations of a frequency source in the time domain. Riley lists 13 types of variances in [Ril08, p. 11].

<sup>&</sup>lt;sup>19</sup> NTP uses the term precision for *the smallest possible increase of time that can be experienced by a program*, i. e., the elapsed time to read the system clock from userland.

The classic N-sample or standard variance

$$s^{2} = \frac{1}{N-1} \sum_{i=1}^{N} (\bar{y}_{i} - \bar{y})^{2} \quad \text{where } \bar{y} = \frac{1}{N} \sum_{i=1}^{N} \bar{y}_{i}$$

(2.14)

should not be used, because it is non-convergent for some common noise types (cf. eq. 2.10).<sup>20</sup>

Five quantities are used by standardization bodies for characterization of time stability [IT96, p. 13] [IEE99]. These are

1. Allan Deviation (ADEV)  $\sigma_y$  is the most common time domain measure of frequency stability. It can be computed from the first differences of M (averaged) frequency samples  $\bar{y}_i$  or, equivalently, from N = M + 1 second differences of phase samples  $x_i$ .

$$\sigma_y^2(\tau) = \frac{1}{2} \left\langle \left( \Delta y \right)^2 \right\rangle \cong \frac{1}{2(M-1)} \sum_{i=1}^{M-1} (\bar{y}_{i+1} - \bar{y}_i)^2$$

(2.15a)

$$\sigma_y^2(\tau) = \frac{1}{2\tau^2} \left\langle \left(\Delta^2 x\right)^2 \right\rangle \cong \frac{1}{2(N-2)\tau^2} \sum_{i=1}^{N-2} (x_{i+2} - 2x_{i+1} + x_i)^2$$

(2.15b)

2. Modified Allan Deviation (MDEV) Mod.  $\sigma_v$  involves an additional phase averaging step

$$\operatorname{Mod.} \sigma_{y}^{2}(m\tau_{0}) = \frac{1}{2(m\tau_{0})^{2}} \left\langle \left(\Delta^{2}\bar{x}\right)^{2} \right\rangle$$

$$\cong \frac{1}{2m^{4}\tau_{0}^{2}(N-3m+1)} \sum_{j=1}^{N-3m+1} \left[ \sum_{i=j}^{j+m-1} (x_{i+2m} - 2x_{i+m} + x_{i}) \right]^{2}$$

(2.16)

where m = 1, 2, ..., |N/3|.

3. Time Deviation (TDEV)  $\sigma_x$

$$\sigma_x^2(\tau) = \frac{\tau^2}{3} \text{Mod.} \, \sigma_y^2(\tau) \tag{2.17}$$

4. Root mean square of Time Interval Error

$$TIE_{rms}(m\tau_0) = \sqrt{\left\langle \left[ x(t + m\tau_0) - x(t) \right]^2 \right\rangle}$$

(2.18)

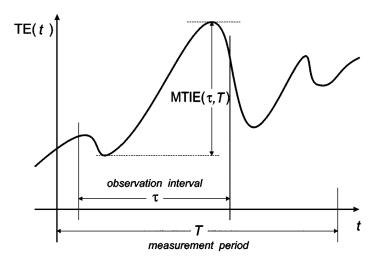

5. Maximum Time Interval Error (MTIE) The maximum time interval error MTIE( $\tau$ ) is defined as a specified percentile,  $\beta$ , of the random variable X.

$$X = \max_{0 \le t_0 \le T - \tau} \left( \max_{t_0 \le t \le t_0 + \tau} [x(t)] - \min_{t_0 \le t \le t_0 + \tau} [x(t)] \right)$$

(2.19)

Fig. 2.3 explains the MTIE definition graphically.

The problem with (2.14) is that the average  $\bar{y}$  is not stationary for  $\alpha < 0$  in (2.10) or  $D \neq 0$  in (2.9) [Ril08, p. 14].

Figure 2.3.: Graphical explanation of MTIE( $\tau$ , T) [BM00]

Double logarithmic plots of the (Modified) Allan Deviation over  $\tau$  are used to identify power law noise processes in clocks, i. e., the exponents  $\alpha$  which dominate  $S_y$  in (2.10) can be determined by observing the slope of the plot [IEE99, p. 12]. Allan Deviation  $\sigma_y$  does not distinguish between white ( $\alpha = 2$ ) and flicker phase noise ( $\alpha = 1$ ) types. The Modified Allan Deviation and the Time Deviation do not have this ambiguity [AAH97].

The Allan deviations are sensitive to systematic effects like diurnal variations, which might mask noise effects [IT96]. Cyclic disturbance causes a distinctive pattern of maxima and minima at the half period and period of the stimulus [Ril03, p. 47]. Unavoidable systematic effects must be adequately filtered before calculating  $\sigma_v$ .

TIE<sub>rms</sub> and MTIE are mainly used by the telecommunication industry [Bre97]. MTIE measures peak time deviation and is therefore very sensitive to transients and outliers [Ril08, p. 33]. Straightforward computation of MTIE scales as  $O(n^2)$ , but an optimized algorithm achieves  $O(n \log n)$  [BM00].

#### 2.3. Hardware Clocks

#### 2.3.1. Crystal oscillators

The crystal oscillator is by far the most important frequency control device (cf. table 2.3). Even inexpensive quartz crystals for wrist watches can have a frequency accuracy of 1 ppm and even better stability  $\sigma_y$  [Lev99]. Low cost, small size, low energy consumption, robust design, and long life are important considerations too.

Since the 1960-ies man-grown single crystals with relatively high purity are used as raw material for resonators. Quartz is a highly anisotropic material. The electromechanical properties of a resonator depend not only on the exact geometry of the resonator, but also strongly on the angles of cut relative to the crystal lattice. An angular difference of one arc-minute makes a significant difference.

2.3. Hardware Clocks

| Technology                              | Units per year    | Avg. unit price \$ | Worldwide market<br>\$ / year |

|-----------------------------------------|-------------------|--------------------|-------------------------------|

| Quartz crystal resonators & oscillators | $3 \times 10^{9}$ | 1                  | $4 \times 10^9$               |

| Rubidium cell frequency standard        | 50000             | 2000               | $100 \times 10^{6}$           |

| Caesium frequency standard              | 500               | 50000              | $25 \times 10^{6}$            |

| Hydrogen maser                          | 20                | 100000             | $2 \times 10^6$               |

Table 2.3.: Frequency control device market (Estimates for 2006) [Vig07, p. 1-2]

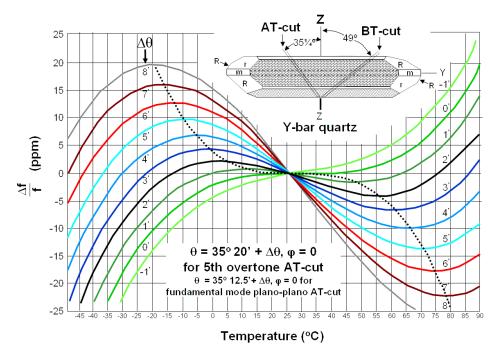

Figure 2.4.: Frequency-Temperature vs. Angle-of-Cut for AT-cut crystal [Vig07, p. 4-44]

Figure 2.4 displays temperature dependent frequency error curves of AT-cut crystals with angle of cut as parameter.

Environmental effects (temperature, humidity, pressure, acceleration, vibration, electromagnetic fields, ionizing radiation...) on frequency have been studied thoroughly [ABC<sup>+</sup>92, WG92]. Because temperature is usually the dominating factor, only temperature compensated cuts are used for frequency control devices. The AT-cut is most popular.<sup>21</sup> Its frequency dependency on temperature is a cubic parabola

$$\frac{\Delta f}{f} = a(T - T_0) + b(T - T_0)^2 + c(T - T_0)^3$$

(2.20)

where  $T_0$  is 25 °C and coefficients a,b,c depend on angle of cut. The inflection point is conveniently near room temperature (25 °C...35 °C).

<sup>&</sup>lt;sup>21</sup> The letter 'T' in the AT- and BT-cuts (and others) stands for "temperature compensated".

The acronyms XO and SPXO denote simple packaged crystal oscillators without any temperature compensation or control. A number of schemes have been developed to mitigate their inherent frequency instability caused by temperature changes.

Commonly used are the following:

**TCXO** use temperature sensitive reactances (thermistor/resistor networks and varactor diodes) to compensate the frequency vs. temperature variations of the crystal. Peak to peak frequency deviations are reduced by a factor of about 100, yielding about  $\pm 0.5$  ppm over a temperature range of -55 °C... 85 °C.  $^{22}$

**MCXO** utilize self-temperature sensing (dual mode) resonators to virtually eliminate thermometry related errors. A microcomputer and digitally stored calibration coefficients are used to control output frequency. About  $\pm 0.03$  ppm (= 30 ppb) over a temperature range of -55 °C... 85 °C are achieved.

**OCXO** For best frequency stability the crystal temperature must be stabilized. In an oven controlled XO the crystal and other temperature sensitive components are enclosed in a thermally insulated container along with a heating element and a temperature sensor.<sup>24</sup> The oven is adjusted to a temperature where the f vs. T graph of the crystal has zero slope.<sup>25</sup> OCXOs reduce frequency variations by a factor > 1000, but at the cost of much higher power consumption. About  $\pm 10$  ppb temperature instability are common. High-end SC-cut units stay within  $\pm 0.1$  ppb over a wide temperature range, have short time stability  $\sigma_{\rm v}(1\,{\rm s}) = 10^{-12}$  and aging of  $10^{-11}$  / day.

Several mechanisms (mass transfer due to contamination, stress relief in the mounting and bonding structure, quartz out-gassing, diffusion, etc.) cause frequency aging [Vig07, p. 4-6]. High quality OCXO and MCXO have considerable less aging than cheaper designs. Table 2.4 shows some typical values and required resynchronization/recalibration intervals for a guaranteed maximum clock error of 25 ms.

#### 2.3.2. Other frequency sources

Crystal oscillators are not well suited for applications where high frequency accuracy or long-term frequency stability are important [Lev99]. The mechanical resonance frequency of a crystal depends on the exact geometry of the artifact and is therefore hard to replicate.

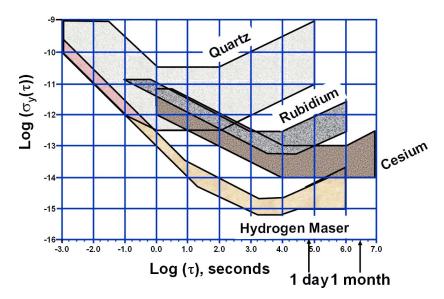

Atomic frequency standards use atomic or molecular resonances. Their stability performance is compared in fig. 2.5. Hydrogen masers provide best medium-time stability while caesium clocks offer best long time stability. There is some overlap in stability and unit price between high end quartz and low end rubidium devices. Rubidium frequency aging is small in comparison with quartz. Caesium devices do not suffer from frequency aging at all.

$<sup>\</sup>frac{1}{22}$  In practice frequency calibration (to compensate aging) degrade f vs. T performance significantly [Vig07, p. 4-52].

<sup>&</sup>lt;sup>23</sup> The fundamental mode  $(f_1)$  and third overtone are excited simultaneously. The beat frequency  $f_{\beta} = 3f_1 - f_3$  depends nearly linearly on crystal temperature. In principle two separate resonators in close thermal contact could be used too [SCF<sup>+</sup>08].

<sup>&</sup>lt;sup>24</sup> High performance units use a *double oven* design, where the outer oven stabilizes the ambient temperature of the inner oven.

<sup>25</sup> Usually SC-cut (stress compensated) crystals are used. The inflection point of their f vs. T graph is about 95 °C. SC-cut crystals have several advantages over AT-cut crystals. They are more expensive to produce because of their double-rotated cut.

2.3. Hardware Clocks 17

| Osc. type | Temp. Stability     | Aging / Day         | Resynchr. | Recalibr.  |

|-----------|---------------------|---------------------|-----------|------------|

| SPXO      | $50 \times 10^{-6}$ | $1 \times 10^{-8}$  | 5 min     | 9 years    |

|           |                     |                     | 8 min     | 200 days   |

| TCXO      | $1 \times 10^{-6}$  | $1 \times 10^{-8}$  | 10 min    | 10 years   |

|           |                     |                     | 4 h       | 80 days    |

| OCXO      | $2 \times 10^{-8}$  | $1 \times 10^{-10}$ | 6 h       | 50 years   |

|           |                     |                     | 4 d       | 1.5 years  |

| MCXO      | $2 \times 10^{-8}$  | $5 \times 10^{-11}$ | 6 h       | 94 years   |

|           |                     |                     | 4 d       | 3 years    |

| RbXO      | $2 \times 10^{-8}$  | $5 \times 10^{-13}$ | 6 h       | not needed |

|           |                     |                     | 4 d       | 300 years  |

Table 2.4.: Resynchronization and recalibration intervals (based on [Vig07, p. 8-10])

Research in optical frequency standards suggests, that reproducible relative frequency accuracies at the  $10^{-17} \dots 10^{-18}$  level should be achievable within a few years [Gil05]. Another current research area is the chip-scale atomic clock for applications requiring atomic timing in portable battery-powered devices [LRV<sup>+</sup>07].

Ceramic resonators perform worse than quartz crystals. Frequency tolerances at 25 °C and frequency variation over the operating temperature range are both typically a few thousand ppm. They should only be used for timing applications where very small savings in unit cost matter more than accuracy.

Several microcontrollers can optionally generate their clock signal from on-chip integrated RC-oscillators. Frequency accuracy is limited to about 2 % (20000 ppm).

#### 2.3.3. Computer clocks

Clocks built into computer systems are almost always of the crystal oscillator & counter type depicted in fig. 2.1. Frequency accuracy and stability requirements for computers are typically low. Low price bulk AT-cut crystals with large frequency tolerances are common.

The Intel x86 PC platform (and hence the general purpose processor of I-SENSE nodes) has several timing sources:

RTC The real time clock is battery backed and keeps time when the PC is powered off. Since the internal counter is not software accessible, the resolution is only one second. The RTC can periodically interrupt the CPU. The interrupt frequency is programmable from 2 Hz to 8192 Hz in powers of two.

**PIT** The Intel 8254 Programmable Interval Timer has three independent 16 bit counters. It has a nominal frequency of 1193181.81 Hz.<sup>27</sup> The nominal frequency can be divided by a programmed 16 bit value to generate periodic interrupts with frequencies down to 18.2 Hz.

<sup>&</sup>lt;sup>26</sup> Among them the popular Atmel AVR and Microchip Technology PIC families of microcontrollers.

<sup>&</sup>lt;sup>27</sup> This is one third of the NTSC color subcarrier frequency—reminiscent of the 1981 color graphics adapter (CGA).

Figure 2.5.: Short term stability ranges of various frequency standards [Vig07, p. 7-5]

**ACPI** The Advanced Configuration and Power Interface Specification requires a 24 bit or 32 bit power management timer running with a fixed frequency of 3.579545 MHz (NTSC-M color subcarrier frequency).

TSC The Time Stamp Counter is 64 bit wide and available on all x86 processors since the Pentium. It is a processor cycle counter (PCC). Its high resolution and the ability to read it in a single machine instruction<sup>28</sup> seem to make it the ideal timer on the PC platform. Unfortunately, power saving measures like idle states and CPU throttling and can make the TSC frequency highly variable.<sup>29</sup> Moreover on multiprocessor systems the per-processor TSCs can proceed at different rates. The TSC cannot be programmed to cause interrupts, which makes it unsuitable for a scheduler clock.

APIC The local APIC (Advanced Programmable Interrupt Controller) timer can interrupt its associated processor when a programmed count is reached. The timer is 32 bit wide. Its frequency is derived from the processor bus clock, divided by a programmable value. It can be configured for one-shot or periodic operation. Dependent on the actual CPU model, the timer may or may not run at a constant rate in different power states and during power state transitions.

**HPET** The High Precision Event Timer (a. k. a. Multimedia Timer before 2002) is a monotonic 64 bit counter running with at least 10 MHz. At least three comparators and match registers and one periodic capable timer are provided. The specification permits large frequency instabilities of  $\pm 500$  ppm over intervals  $\geq 1$  ms and  $\pm 2000$  ppm over intervals  $\leq 100$   $\mu$ s. HPET is not available on older hardware and unsupported by older operating system releases.

Availability, resolution, width, interrupt features, and access/reprogramming speed vary a lot between the above hardware timers. Besides, several of the timers are BIOS managed and quite a lot of broken

<sup>&</sup>lt;sup>28</sup> RDTSC or RDTSCP. The latter instruction prevents out of order execution.

<sup>&</sup>lt;sup>29</sup> Spread-spectrum clocking—a technique for electromagnetic interference reduction—introduces clock frequency modulation too. [HFB94]

2.3. Hardware Clocks 19

implementations have been reported. It is therefore impossible to choose an optimal timer without detailed knowledge of the actual hardware/BIOS combination and/or testing. Some operating systems consequently choose the best system timer during the start-up process after probing the hardware [Kam02].

Built-in clock hardware on other platforms varies, but the combination of crystal oscillator and counter is always present. There is great variation in other hardware details like programmable prescalers or PLLs, availability and number of comparators, one shot and periodic interrupt facilities, and speed and level of software access to timer hardware registers. The timer hardware details of I-SENSE signal processor boards are described in section 4.1.1 on page 47.

Many microcontrollers have even more elaborate timer hardware, like up/down counters, external event counters, and PWM output modes. A highly useful feature for timekeeping purposes, which is present in many microcontrollers, <sup>30</sup> is the capture register. By capturing timestamps of (external) events in hardware, the timing uncertainty associated with interrupt latency is avoided. Unfortunately, neither commercial off the shelf (COTS) PC hardware nor the I-SENSE DSP boards are equipped with capture registers.<sup>31</sup>

There is little recent literature about the quality of COTS computer clocks. Most of it does neither include temperature data nor specify whether the machines have been operated in air conditioned rooms.

Marouani and Dagenais report accuracy and stability data on the CPU clocks of some 30 Intel and AMD systems with nominal CPU frequencies between 266 MHz and 2.4 GHz [MD08]. CPU frequency offset from nominal frequency was a few thousand ppm. Frequency variation between eight equal Pentium IV models spans 29 ppm. A temperature change from 28 °C to 47.25 °C caused a -8.3 ppm change of CPU frequency, diurnal variation was 0.74 ppm.<sup>32</sup>

Kohno et al. used TCP timestamps to *remotely* measure clock frequency [KBC05]. They found that individual machines show only 1–2 ppm clock skew over time, but found some 50 ppm variation between individual machines, even identical models.

The static rate difference calibration mentioned in section 1.1 resulted in a maximum rate difference of 142 ppm between a management PC and four I-SENSE DSP cards.

The author's measurement of an I-SENSE node in a laboratory *without* air conditioning is depicted in fig. 2.6. Frequency variation over 24 hours stayed below 2 ppm but was larger over several days. The lower (blue) curve and the scale on the right y-axis show the normalized rate difference between the system clock of the general purpose processor and a DSP node. Both processors/oscillators were located within the same case and thus thermally coupled. This caused an effect similar to common mode rejection—the change in skew *between* both clocks was only about 0.1 ppm.<sup>33</sup>

$<sup>^{30}\,\</sup>mathrm{E.\,g.}$ , the Atmel AVR or TI MSP430 controllers.

<sup>&</sup>lt;sup>31</sup> A main reason why PC based precision timing applications always need more additional hardware (timing cards) than only an external reference clock.

<sup>&</sup>lt;sup>32</sup> Only one system has been measured.

<sup>&</sup>lt;sup>33</sup> A constant bias of 22 ppm has been removed. The observed effect is helpful for inter-node synchronization, but it depends entirely on the *coincidental* matching of the f-versus-T characteristics of both crystals. (cf. fig. 2.4 on page 15 and [SCF<sup>+</sup>08].)

Figure 2.6.: Frequency variation of a computer clock over a week.

#### 2.3.4. External reference clocks

Synchronization of computer networks to external timescales like UTC requires injection of reference time into the network. The points of injection are external reference clocks that are interfaced to network nodes. Many national time standard laboratories attach atomic clocks to public NTP servers in order to inject their realizations of UTC into the Internet. Most external clocks are either radio controlled clocks or GPS time receivers.

**Radio clocks** are synchronized to terrestrial time signals. Many countries operate longwave time signal transmitters like WWVB at 60 kHz in the U.S., DCF77 at 77.5 kHz in Germany, and TDF at 162 kHz in France. The signal range is between 2000 km (DCF77 50 kW) and 3500 km (TDF 2 MW). Small indoor antennas are usually adequate. Cheap, narrow bandwidth receivers have only accuracies in the 5–25 ms range. Commercial correlation receivers achieve about 50 μs when they are calibrated for the transmitter to receiver distance.

**GPS receivers** can operate worldwide but antennas need good sky view (and therefore rooftop access is frequently required). Even cheap units have 1 μs accuracy. Commercial quality units achieve about 50 ns accuracy and are equipped with Time Receiver Autonomous Integrity Monitoring (TRAIM) to protect against faulty satellite signals.

**LORAN** (LOng RAnge Navigation) is a terrestrial longwave navigation system that uses high peak power pulses at 100 kHz [RSJ<sup>+</sup>05]. It was introduced in 1957 and is used mainly by the U. S., Europe, and Japan. GPS performs much better than the present LORAN-C system, however the U. S. have modernized the system to achieve better navigation and timing performance. The enhanced LORAN (eLORAN) system can be used as a timing source with about 100 ns accuracy.<sup>34</sup> The eLORAN time and frequency accuracy can support almost all civilian applications. E-Loran can be used as a local backup/complement to GPS.

<sup>&</sup>lt;sup>34</sup> This requires receiver and antenna calibration and LORAN data channel (LDC) corrections.

2.4. Software Clocks 21

#### 2.3.5. Interfacing external clocks

At the physical layer the clock-computer interface is frequently realized as pulse per second (PPS) signals. Only minimal add-on hardware (a cable and sometimes a level converter) is needed, because most computers can be programmed to trigger an interrupt when a signal flank arrives at certain parallel or serial port pins.<sup>35</sup> A PPS API has been defined and free implementations for some POSIX systems exist.<sup>36</sup>[MMB+00, MK00] Since PPS signals only mark the start of a second but do not tell which second begins, an additional serial or USB connection is needed.

Cheap radio clocks and several navigation-only GNSS receiver models (through the NMEA protocol) use a serial link alone. Because of the relatively slow communication speed and (hardware and software) buffering of serial data streams a large timing uncertainty of tens of milliseconds results.

Precision timing hardware (like PCI timing cards) normally uses IRIG-B time code signals to synchronize with external reference clocks [IRI04].

#### 2.4. Software Clocks

This section deals with clocks from the viewpoint of software. Application programs use time related APIs rather than accessing timer hardware directly. System software isolates applications from idiosyncrasies of actual timer hardware by providing clock abstractions.

#### 2.4.1. Operating system view

Operating system provided clocks can be categorized into three classes:

Counter register read access is the most simple API. Examples are library wrappers around PCC read instructions or the <code>QueryPerformanceCounter</code> function in Microsoft Windows. The counter frequency is either available from an API<sup>37</sup> or must be obtained from a hardware specification. Since the epoch is the time of the last system reset, these clocks are rather used for time interval measurements than for providing UTC. Because of low clock access overheads and high frequencies, these clocks are ideal for execution time profiling and similar performance measurements.

**Periodic timer interrupts** are used by virtually all operating systems. Windows system time is implemented this way. The interrupt service routine increments a software counter. Both the interrupt events and the intervals between them are conventionally called *ticks*. The timer interrupt frequency limits clock precision. Most older Unix/Linux systems used 100 Hz (10 ms). As processor speeds have increased, higher frequencies up to 1000 Hz are nowadays more

<sup>&</sup>lt;sup>35</sup> On commodity PCs either the DCD pin (carrier detect) of a serial port or the ACK pin of a parallel port is used.

<sup>&</sup>lt;sup>36</sup> The NTP reference implementation supports the PPS API on Windows too.

<sup>&</sup>lt;sup>37</sup> On many Windows systems the QueryPerformanceFrequency function returns 3.579545 MHz—the ACPI power management timer frequency.

common.<sup>38</sup> At the time of this writing the Microsoft Windows system clock still uses either 100 Hz or 64 Hz.

**Interpolation schemes** combine the two previously described approaches in order to improve clock resolution. A periodic interrupt is used for basic time keeping, and a high frequency counter is used to interpolate between ticks.

To achieve increased resolution the Windows port of the NTP reference implementation does system clock interpolation at the application layer (i. e., outside the kernel). The implementation uses the multimedia timer API to get 1000 callbacks per second from the kernel. The performance counter is used to interpolate between callback events. A drawback of this approach is that callback invocation may be delayed for several milliseconds during phases of heavy system load.<sup>39</sup>

#### 2.4.2. Clock phase and rate adjustment

Figure 2.7.: Clock adjustment sawtooth error [Mil06b, p. 180].

The frequency offsets of computer hardware clocks are in a range from a few to a few hundreds ppm. Since even a rate offset of 1 ppm leads to a time error of 86.4 ms/day, some means of correction is needed—at least for clocks tracking wall clock time.<sup>40</sup>

Setting the time to a new value is problematic, because it violates assumptions about a continuous timescale. Stepping time backwards is known to confuse application programs. Clock steps are hence avoided and (small) phase corrections are made by changing the clock rate instead. The time a clock needs to run with increased or decreased rate to achieve a given phase correction is called the *amortization interval*.

Unix systems use the adjtime system call to make small adjustments to the system time. This amortizes the given signed time offset by using an increment that is slightly larger or smaller than normal. The kernel reverts automatically to the standard increment as soon as the adjustment is complete. Unix typically increases or decreases the rate during adjustments by 500 ppm, i.e., it

<sup>&</sup>lt;sup>38</sup> Periodic interrupts on an otherwise idle machine cause wakeups from power-saving states, which is detrimental to power efficiency. Clock ticks also add to "system noise". The Linux kernel is therefore moving away from this traditional design. [TEFK05, SPV07]

<sup>&</sup>lt;sup>39</sup> A slightly modified version of this interpolation clock is used for the I-SENSE synchronization process on general purpose processor nodes.

<sup>&</sup>lt;sup>40</sup>Clocks that measure the system uptime(e.g., GetTickCount on Windows) usually cannot be phase or rate adjusted.

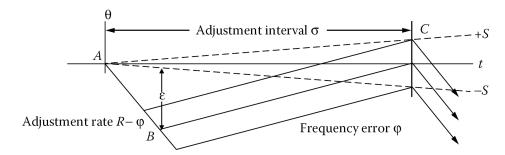

takes  $2000 \,\mathrm{s}$  (more than 33 minutes) to amortize one second. Only three clock rates are available, the unadjusted rate with a frequency error (line  $\overline{BC}$  in fig. 2.7), the same rate reduced by -500 ppm (line  $\overline{AB}$ ), and increased by -500 ppm. The  $\overline{ABC}$  sawtooth of fig. 2.7 has to be repeated permanently (and adjtime calls made at A) in order to keep the offset error low.

The Windows scheme for clock adjustment offers more flexibility for rate control, but there is no API for amortized offset corrections. The SetSystemTimeAdjustment function sets the increment added to the time-of-day clock at each clock interrupt. This allows arbitrary system clock rates, but since Windows system time has 100 ns resolution, the granularity of possible rates is only 10 ppm/6.4 ppm at the common 100 Hz/64 Hz tick rates.

POSIX systems with kernel support for NTP<sup>41</sup> allow very fine grained rate settings and offset corrections with the ntp\_adjtime system call.

#### 2.4.3. Application view

On general purpose operating systems direct access to the timer hardware is not possible.<sup>42</sup> Clocks that are provided by the OS are used.

| OS       | Time format      | Size                      | Resolution          | Precision             | Wrap around      |   |

|----------|------------------|---------------------------|---------------------|-----------------------|------------------|---|

| Windows  | System Time      | $8 \times 16  \text{bit}$ | 1 ms                | ca. 10 ms             | 65536 years      |   |

|          | File Time        | $2 \times 32  \text{bit}$ | 100 ns              | ca. 10 ms             | 58454 years      |   |

|          | MS-DOS Time      | $2 \times 16  \text{bit}$ | 2 s                 | 2 s                   | 128 years        |   |

|          | Windows Time     | 32 bit                    | 1 ms                | ca. 10 ms             | 49.7 days        | a |

|          | MM Timers        | 32 bit                    | 1 ms                | $\geq 1  \mathrm{ms}$ | 49.7 days        |   |

|          | HR Timer         | 64 bit                    | 279.4 ns            | 279.4 ns              | 163300 years     | b |

| DSP/BIOS | Highres Timer    | 32 bit                    | 13.33 ns            | 13.33 ns              | 57.27 sec        | с |

|          | Lores Timer      | 32 bit                    | 1 ms                | 1 ms                  | 49.7 days        | d |

| NTP      | internal formats | 64128 bit                 | 1 μs <i>or</i> 1 ns | ≥1 ns                 |                  | e |

|          | wire format      | 64 bit                    | 232.8 ps            |                       | 136 years        |   |

| POSIX    | struct timeval   | $2 \times 32  \text{bit}$ | 1 μs                | ≥1 μs                 | 136 years        | f |

|          | struct timespec  | 64 bit+32 bit             | 1 ns                | $\geq 1 \text{ ns}$   | $>10^{11}$ years | f |

Table 2.5.: Time representations in various APIs

<sup>&</sup>lt;sup>a</sup> Epoch is system boot, i. e., the system uptime is returned.

$<sup>^{\</sup>rm b}$  Assuming QueryPerformanceFrequency() =  $3.579545\,\mathrm{MHz}$

<sup>&</sup>lt;sup>c</sup> The timer frequency is  $f_{CPU}/4$  or  $f_{CPU}/8$  depending on CPU model. The values shown are for an I-SENSE DSP node with a 600 MHz TMS320C64X CPU.

<sup>&</sup>lt;sup>d</sup> The low-resolution timer period is configurable with a 1 ms default value.

<sup>&</sup>lt;sup>e</sup> Either micro- or nanosecond resolution is used dependent on a status flag.

<sup>&</sup>lt;sup>f</sup> The standard does not specify the size of the integer seconds part (time\_t).

<sup>&</sup>lt;sup>41</sup> Solaris, \*BSD, Linux, and Darwin.

<sup>&</sup>lt;sup>42</sup> Unless one goes through the hassles of developing, maintaining, and deploying a device driver.

From the application programmer's view, it is irritating that so many different date-time and time interval representations with varying resolution and precision are provided. Table 2.5 shows some examples. The I-SENSE time synchronization software has to deal with several of the tabled time formats. Conversion between formats must scale resolutions and consider different epochs (cf. table 2.6).<sup>43</sup>

| Timescale | Epoch      |

|-----------|------------|

| Windows   | 1601-01-01 |

| MS-DOS    | 1980-01-01 |

| NTP       | 1900-01-01 |

| POSIX     | 1970-01-01 |

| .NET      | 0001-01-01 |

| MacOS     | 1904-01-01 |

Table 2.6.: Epochs of some computer timescales

API documentation is frequently lacking important specifications. Answers to the following questions often require additional research or testing:

**Precision** What is the minimum time interval between clock increments?

**Monotonicity** Is the clock (strictly) monotonic?

**Accuracy** Is the clock disciplined, i. e., rate and offset controlled? If yes: How does this affect monotonicity and rate accuracy? Can the synchronization state be obtained?

Obtaining answers to questions about clock *reliability*<sup>44</sup> and clock *access overhead* most often requires running test programs on the target hardware.

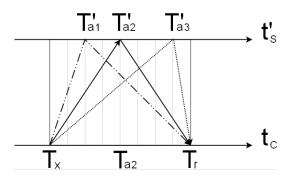

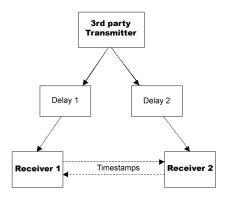

### 2.5. General Clock Synchronization Model