## Low Resource Hardware Implementation of an Edwards Curve Digital Signature Algorithm

Jeremias Peter Kleer jeremias.kleer@student.tugraz.at

Institute for Applied Information Processing and Communications (IAIK) Graz University of Technology Inffeldgasse 16a 8010 Graz, Austria

#### Master Thesis

Supervisor: Dipl.-Ing. Dr.techn. Michael Hutter Supervisor: Dipl.-Ing. Dr.techn. Erich Wenger Assessor: Ao.Univ.-Prof. Dipl.-Ing. Dr.techn. Karl-Christian Posch

Senat

Deutsche Fassung: Beschluss der Curricula-Kommission für Bachelor-, Master- und Diplomstudien vom 10.11.2008 Genehmigung des Senates am 1.12.2008

### EIDESSTATTLICHE ERKLÄRUNG

|                              | gende Arbeit selbstständig verfasst, andere als die<br>und die den benutzten Quellen wörtlich und inhaltlich<br>acht habe. |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Graz, am                     | (Unterschrift)                                                                                                             |

| Englische Fassung: STATUTORY | / DECLARATION                                                                                                              |

|                              | endently, that I have not used other than the declared marked all material which has been quoted either                    |

| date                         | (signature)                                                                                                                |

## Acknowledgements

I want to thank Karl-Christian Posch, Michael Hutter and Erich Wenger of the Graz University of Technology for their support, their patience and for making this thesis possible.

I also want to thank Angelika Gerstmann and my family for their exceptional patience, support and love.

In addition I want to thank Eva Gerstmann for her time and commitment when correcting my English.

### Abstract

Cryptography has become substantial in the digital world. Beside encryption, authentication is a major topic within cryptography. Authentication is important, for instance, in the world wide web where online banking or services of authorities are used.

In the past years, authentication has reached very small devices. They are accessing the Internet and use the same services where authentication is required. Such small devices are often battery powered and have limited resources. In this environment, performing the hard calculations of authentication is a crucial issue and can hardly be performed by a general processor. Here, application specific integrated circuits (ASIC) have the advantage to be tailored to one specific function. ASICs are dedicated hardware modules and perform calculations in a very efficient way. Efficiency in this context is often measured in the area-time product which allows to judge the trade-off between the necessary circuit area against the time the execution of performed task takes.

To perform authentication, several cryptographic systems and protocols are available and are based on different mathematical hard problems. For constrained devices, the elliptic curve discrete logarithm problem is very well suited. Therefore the standardized and approved Elliptic Curve Digital Signature Algorithm (ECDSA) enjoys great popularity. Beside this, Bernstein et al. [8] in 2011 introduced an alternative digital signature scheme: The Edwards-curve Digital Signature Algorithm (EdDSA). On the one hand it has advantages over ECDSA regarding the speed and on the other hand it circumvents security issues of ECDSA.

The key difference of EdDSA and ECDSA is the usage of twisted Edwards-curves rather than elliptic curves in Weierstrass form. These curves have a different defining equation and thus the point addition and point doubling formulas differ. Beside the definition of the general EdDSA the Ed25519-SHA512 was introduced in [8] which has all necessary parameters chosen for an efficient implementation.

In this thesis, a low resources ASIC hardware implementation is presented which is able to perform the scalar multiplication necessary for the Ed25519-SHA512. The implementation supports different word widths and those are evaluated for the most efficient ones. The synthesis on the  $0.35\,\mu\mathrm{m}$  CMOS-process technology of ams AG¹ revealed the following results for different word widths (the area values in the parentheses include the area of the memory):  $7.4~(44.4)~\mathrm{kGE}$  and  $2.04\cdot10^6$  cycles for 16 bits, 12 (48.8) kGE and  $0.8\cdot10^6$  cycles for 32-bit hardware, and 27.9 (66.1) kGE and  $0.414\cdot10^6$  cycles for 64 bits.

**Keywords:** EdDSA, Twisted Edwards-Curves, Digital Signature, ASIC, Hardware Implementation, Scalar Multiplication

<sup>&</sup>lt;sup>1</sup>ams AG ist the new name of the company formerly called austriamicrosystems AG.

## Kurzfassung

In der digitalen Welt ist Kryptographie zu einem wesentlichen Bestandteil geworden. Dabei spielt neben der Verschlüsselung insbesondere die Authentifizierung eine wichtige Rolle. Diese ist zum Beispiel im World Wide Web wichtig - speziell etwa beim Internet-Banking oder bei Online-Diensten von Behörden.

Heutzutage wird Authentifizierung auch auf kleinsten Geräten benutzt. Über sie besteht Zugang zum Internet und es ist möglich, auf Angebote zuzugreifen, die eine Authentifizierung erfordern. Diese Geräte laufen oft mit Batterie und bieten daher nur begrenzte Ressourcen. Da die zur Authentifizierung nötigen Berechnungen aufwändig sind, stellen sie hier einen kritischen Aspekt dar - sie können einen universellen Prozessor überfordern. In solchen Fällen empfiehlt sich daher die Benutzung von anwendungsspezifischen integrierten Schaltungen (ASIC). Es handelt sich dabei um speziell abgestimmte Hardware-Module, die auf eine Aufgabe besonders zugeschnitten sind und diese effizient berechnen. Gemessen wird die Effizienz hierbei oft anhand des Flächen-Zeit-Produkts. Dieses ermöglicht die Beurteilung des Kompromisses zwischen einerseits einer raschen Berechnung und andererseits einer kleinen Fläche der Schaltung.

Für die Authentifizierung stehen einige kryptographische Systeme und Protokolle zur Verfügung, die auf unterschiedlichen mathematischen Problemen basieren. Für eingeschränkte Geräte ist der diskrete Logarithmus über elliptische Kurven gut geeignet, der beim Elliptische Kurven Digitalen Signatur Algorithmus (ECDSA) benutzt wird. Daneben hat Bernstein et al. [8] eine Alternative im Jahr 2011 präsentiert - den Edwards-Kurven Digitalen Signatur Algorithmus (EdDSA) - der Geschwindigkeits- und Sicherheitsvorteile bietet.

Der Hauptunterschied zwischen EdDSA und ECDSA ist die Benutzung von Twisted Edwards Kurven anstatt von Kurven in Weierstraß-Form. Diese Kurven haben eine andere Kurvengleichung und deshalb auch abweichende Gleichungen für die Punktaddition und -verdopplung. Neben der allgemeinen Definition von EdDSA wurde in [8] auch Ed25519-SHA512 präsentiert, bei dem die nötigen Parameter in Hinblick auf eine effiziente Implementierung gewählt wurden.

In dieser Arbeit wird eine ressourcenschonende ASIC-Hardware-Umsetzung präsentiert, die für Ed25519-SHA512 die nötige Skalar-Multiplikation berechnen kann. Sie unterstützt mehrere Wortbreiten, die auf ihre Effizienz evaluiert wurden.

Die Synthese mit der  $0.35 \,\mu\mathrm{m}$  Technologie von ams  $\mathrm{AG^2}$  hat zu folgenden Ergebnissen geführt (die Flächen in den Klammern sind inklusive der Fläche für den Speicher): 7.4 (44.4) kGE und  $2.04 \cdot 10^6$  Takte bei einer 16-Bit-Architektur, 12 (48.8) kGE und  $0.8 \cdot 10^6$  Takte bei 32 Bits, und 27.9 (66.1) kGE und  $0.414 \cdot 10^6$  Takte bei 64 Bits.

<sup>&</sup>lt;sup>2</sup>ams AG ist der neue Name der austriamicrosystems AG.

$\bf Stichw\"{o}rter:$  EdDSA, Twisted Edwards-Curves, Digitale Signatur, ASIC, Hardware Umsetzung, Skalar Multiplikation

## Contents

| Li            | st of           | Figure  | es                                                  | ix        |

|---------------|-----------------|---------|-----------------------------------------------------|-----------|

| $\mathbf{Li}$ | st of           | Tables  |                                                     | x         |

| $\mathbf{Li}$ | st of           | Algori  | thms                                                | xi        |

| 1             | Intr            | oducti  |                                                     | 1         |

|               | 1.1             | Outline | e                                                   | 2         |

| <b>2</b>      | $\mathbf{Intr}$ | oducti  | on to Cryptography                                  | 3         |

|               | 2.1             | Symme   | etric-key Cryptography                              | 5         |

|               |                 | 2.1.1   | Key Distribution and Management                     | 6         |

|               |                 |         | 2.1.1.1 Key Distribution                            | 7         |

|               |                 |         | 2.1.1.2 Key Management                              | 7         |

|               | 2.2             | Public- | -key Cryptography                                   | 8         |

|               |                 | 2.2.1   | Concept of Public-key Cryptography                  | 8         |

|               |                 | 2.2.2   | Exemplary Goals                                     | 8         |

|               |                 | 2.2.3   | Mathematical Hard Problems                          | 9         |

|               |                 | 2.2.4   | The RSA Cryptographic Scheme                        | 9         |

|               |                 | 2.2.5   | Elliptic Curve Discrete Logarithm Problem           | 11        |

|               |                 |         | 2.2.5.1 Groups And Finite Fields                    | 11        |

|               |                 |         | 2.2.5.2 The Discrete Logarithm Problem              | 13        |

|               |                 |         | 2.2.5.3 Elliptic Curves Over Finite Fields          | 13        |

|               |                 |         | 2.2.5.4 The Discrete Logarithm With Elliptic Curves | 17        |

|               |                 |         | 2.2.5.5 Curve types                                 | 18        |

|               |                 |         | 2.2.5.6 Coordinate systems                          | 19        |

|               | 2.3             | Securit | y Measurement                                       | 20        |

|               | 2.4             |         | ary                                                 | 21        |

|               |                 |         | •                                                   |           |

| 3             | Edv             |         |                                                     | <b>22</b> |

|               | 3.1             | EdDSA   | A Parameters                                        | 22        |

|               |                 | 3.1.1   | Curve                                               | 23        |

|               |                 | 3.1.2   | Hash Function                                       | 23        |

|               |                 | 3.1.3   | Primes                                              | 24        |

|               |                 | 3.1.4   | b-Bit Point Encoding                                | 25        |

|               | 3.2             | Signati | ure Operations                                      | 25        |

|               |                 | 3.2.1   | Signature Generation                                | 25        |

|               |                 | 3.2.2   | Signature Verification                              | 26        |

|     | 3.3 | Security Considerations                              | 26         |

|-----|-----|------------------------------------------------------|------------|

| 3.4 |     | Differences between EdDSA and ECDSA                  |            |

|     | 3.5 | Ed25519-SHA512                                       | 28         |

|     |     | 3.5.1 The Arithmetic of Ed25519                      | 28         |

|     |     | 3.5.1.1 Integer Arithmetic                           | )(         |

|     |     | 3.5.1.2 Finite-Field Arithmetic                      | 3(         |

|     |     | 3.5.1.3 Group Operations                             | 34         |

|     |     | 3.5.1.4 Scalar Multiplication                        | <b>}</b> [ |

| 4   | Har | dware Implementation 3                               | 38         |

|     | 4.1 | Goals                                                | 38         |

|     | 4.2 | Related Work                                         |            |

|     | 4.3 | IAIK Design Flow                                     | 11         |

|     |     | 4.3.1 Compilation, Synthesis and Place-and-Route     |            |

|     |     | 4.3.2 Simulation                                     |            |

|     | 4.4 | The Architecture                                     | 12         |

|     |     | 4.4.1 Word-Width Consideration and Limitations       | 14         |

|     | 4.5 | The Interface                                        | 16         |

|     |     | 4.5.1 General Considerations and Characteristics     | 16         |

|     |     | 4.5.2 Bus Access                                     | 16         |

|     |     | 4.5.3 Special Addresses                              | 51         |

|     |     | 4.5.4 Command Addresses                              | 52         |

|     |     | 4.5.4.1 Loading Addresses of Operands                | 53         |

|     |     | 4.5.4.2 Integer Arithmetic                           | 53         |

|     |     | 4.5.4.3 Finite Field                                 | 54         |

|     |     | 4.5.4.4 Group Arithmetic and Scalar Multiplication 5 | 54         |

|     | 4.6 | The Controlpath                                      | 55         |

|     |     | 4.6.1 State Machine                                  | 55         |

|     |     | 4.6.2 Details of Operations                          | 57         |

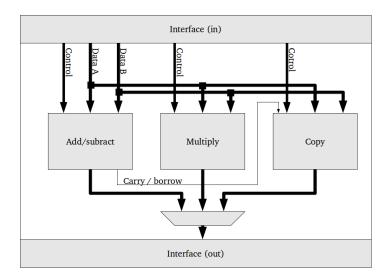

|     | 4.7 | The Datapath                                         | 31         |

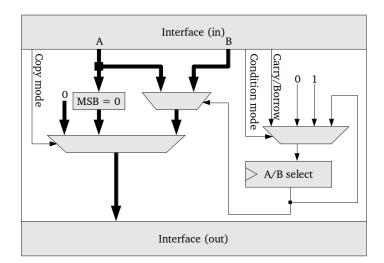

|     |     | 4.7.1 Copy Operation                                 | 31         |

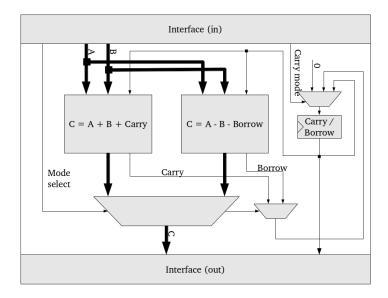

|     |     | 4.7.2 Addition and Subtraction                       | 33         |

|     |     | 4.7.3 Multiplication                                 | 33         |

|     | 4.8 | The Memory                                           | 35         |

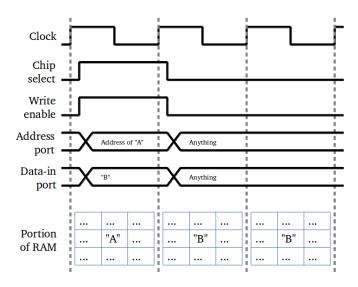

|     |     | 4.8.1 Random Access Memory                           | 35         |

|     |     | 4.8.2 Read-Only Memory                               | 36         |

|     | 4.9 | Verification by Software                             | 36         |

|     |     | 4.9.1 Highlevel Model                                | 37         |

|     |     | 4.9.1.1 Design-Flow Integration                      | 38         |

|     |     | 4.9.1.2 Verification of the Highlevel Model          | 38         |

|     |     | 4.9.2 Test Bench                                     | 36         |

|     |     | 4.9.2.1 Hexadecimal-String Manipulation 6            | 36         |

|     |     | 4.9.2.2 Stimuli, Readouts and Checks                 | 7(         |

| 5   | Res | sults 7                                              | 72         |

|     | 5.1 | Synthesis Aspects                                    | 72         |

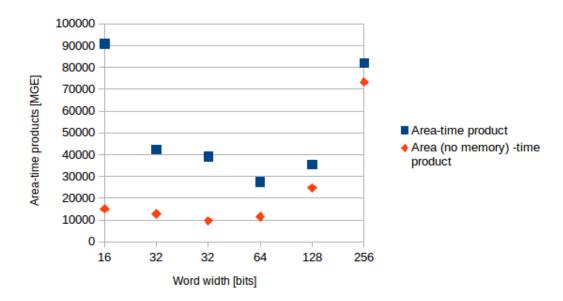

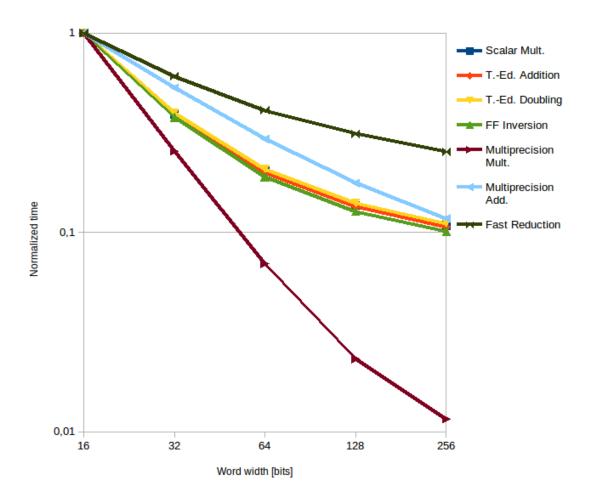

|     | 5.2 | Varying Word Width                                   |            |

|     | 5.3 | v e                                                  | 76         |

| 6            | Conclusion               | <b>7</b> 9 |

|--------------|--------------------------|------------|

|              | 6.1 Future Work          | 80         |

| $\mathbf{A}$ | Definitions              | 82         |

|              | A.1 Abbreviations        | 82         |

| В            | Technical Specifications | 83         |

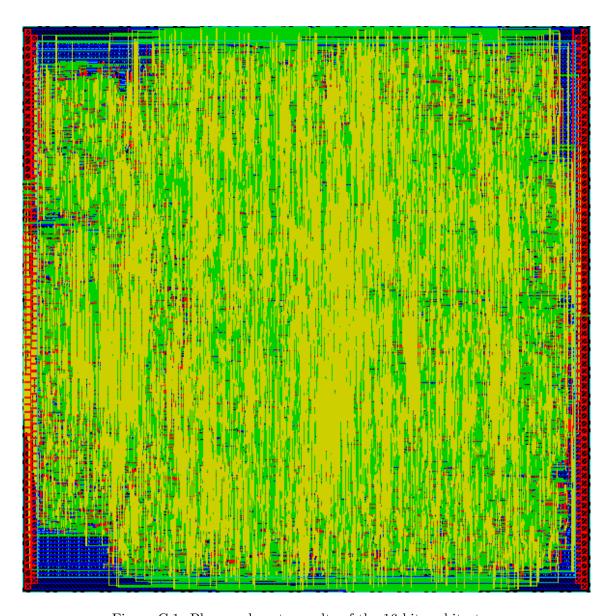

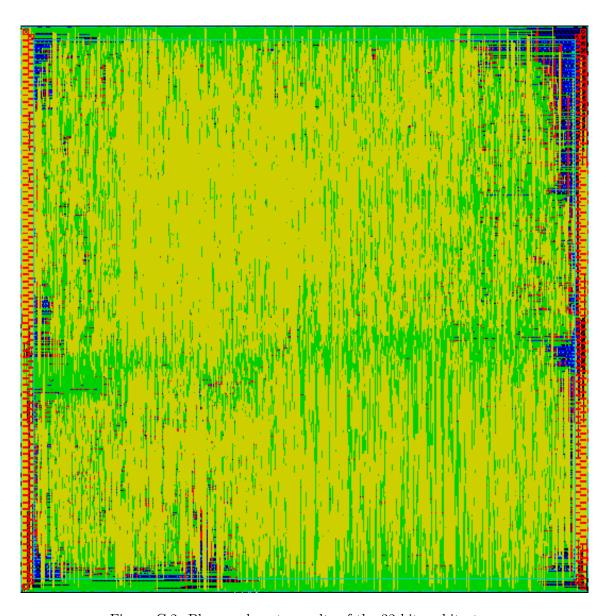

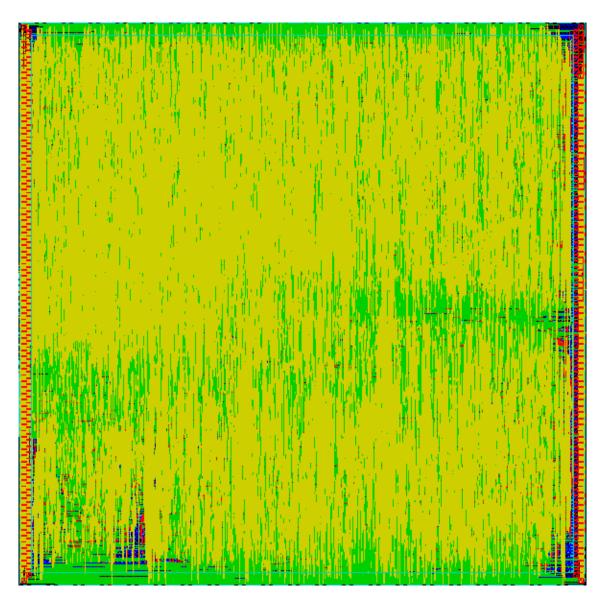

| $\mathbf{C}$ | Final Chip Layouts       | 85         |

| Bi           | bliography               | 89         |

# List of Figures

| 2.1  | Communication in an insecure environment                          | 5  |

|------|-------------------------------------------------------------------|----|

| 2.2  | Curve $y^2 = x^3 - x$                                             | 14 |

| 2.3  | Curve $y^2 = x^3 - x + 1$                                         |    |

| 2.4  | Curve $y^2 = x^3 - x + 1$ with 4 different intersections          |    |

| 2.5  | Twisted Edwards curve $10x^2 + y^2 = 1 + 6x^2y^2$                 |    |

| 2.6  | Montgomery curve $3y^2 = x^3 + 10x^2 + x$                         |    |

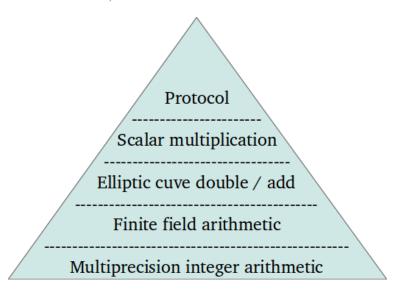

| 3.1  | Layers of arithmetic                                              | 29 |

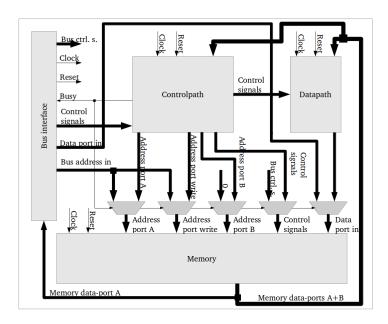

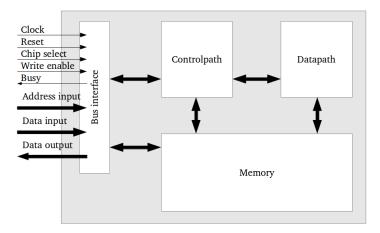

| 4.1  | Illustration of the architecture                                  | 43 |

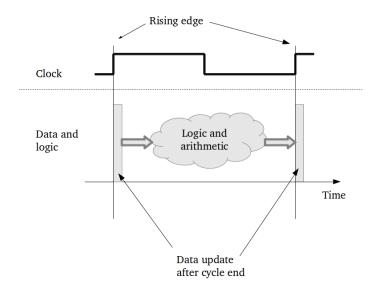

| 4.2  | Illustration of a synchronous design                              | 44 |

| 4.3  | Illustration of the architecture including the interface          | 46 |

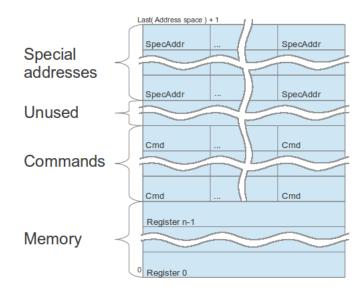

| 4.4  | Schematic illustration of the address space                       | 48 |

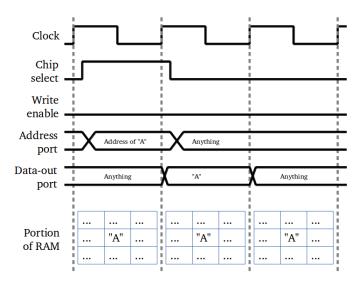

| 4.5  | Illustration of a read bus-access from the RAM                    | 50 |

| 4.6  | Illustration of a write bus-access into the RAM                   | 51 |

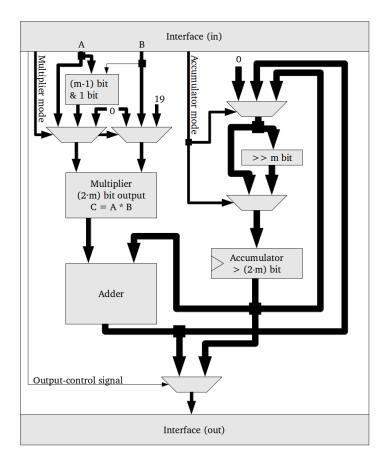

| 4.7  | Illustration of the datapath with its modules and signals         | 62 |

| 4.8  | The copy operation's modes                                        | 62 |

| 4.9  | The addition and subtraction module in the datapath               | 63 |

| 4.10 | The multiplication module with the multiplier and the accumulator | 64 |

| 5.1  | The area-time products for different word widths                  | 74 |

| 5.2  | The normalized execution times of the different operations        | 77 |

| C.1  | Place-and-route results of the 16-bit architecture                | 86 |

| C.2  | Place-and-route results of the 32-bit architecture                | 87 |

| C.3  | Place-and-route results of the 64-bit architecture                | 88 |

## List of Tables

| 2.1 | Excerpt of NIST's comparison of cryptographic schemes              | 21 |

|-----|--------------------------------------------------------------------|----|

| 5.1 | Synthesis results for different word widths                        | 73 |

| 5.2 | The synthesized areas of the single components in gate equivalents | 75 |

| 5.3 | The amount of cycles for the single operations                     | 76 |

| 5.4 | The area, time and area-time product                               | 78 |

# List of Algorithms

| 1 | Key-pair generation                                                          | 25 |

|---|------------------------------------------------------------------------------|----|

| 2 | Signature generation                                                         | 26 |

| 3 | Signature verification                                                       | 26 |

| 4 | Inversion by exponentiation                                                  | 33 |

| 5 | Product-scanning form of a multiprecision multiplication with an accumulator | 58 |

| 6 | Twisted-Edwards addition                                                     | 59 |

| 7 | Twisted-Edwards doubling                                                     | 59 |

| 8 | Modified twisted-Edwards addition                                            | 60 |

| 9 | Modified twisted-Edwards doubling                                            | 61 |

### Chapter 1

### Introduction

Authentication is a fundamental process within the society and is required for any authority and administration. In the digital world this process is conveniently solved by public key cryptography (PKC) in which an entity can prove that the information is indeed originated by itself. For example, an entity can sign in on an administration website and fill in a form or receive information that should not be readable for the public. The PKC is based on mathematical hard problems that cannot be reversed or are computationally infeasible. An entity generates a key pair with one private and one public key. It can then use the private key to prove that it is indeed the one.

For PKC the elliptic curve discrete logarithm problem has been identified to be suitable to offer appropriate security for rather small secrets and to therefore be very efficient compared to other mathematical hard problems such as the integer factorization problem or the usual discrete logarithm problem. In this context, the ECDSA is a popular cryptographic system. It is standardized by the American National Standards Institute(ANSI), approved by NIST and even used for high security within governments.

The digital world has evolved and cryptographic applications are not limited to powerful personal computers anymore. Cryptography has become a topic for even the smallest electronic devices. There are mobile phone and even watches with access to the Internet and thus the problem arises that these constrained devices need cryptography. The limited computational capabilities of constrained devices implies thus low resource consumptions and efficiency. Those requirements imply the use of ASICs.

The ECDSA is based on certain elliptic curves and has certain mathematical implications and algorithmic requirements. In 2007, Edwards introduced in [13] a new form of elliptic curves that offer more efficient algorithmic with additionally improved security against attacks. Bernstein et al. in [11], based on Edwards curves, introduced twisted-Edwards curves and further extended the number of elliptic curves that can be used for the efficient algorithms. Bernstein et al. in [8] then introduced the Edwards-Curve Digital Signature Algorithm (EdDSA), a digital signature algorithm which is related to the ECDSA but uses twisted-Edwards curves and has some algorithmic modifications that improve security.

For the rather young and not standardized EdDSA, no hardware implementation as ASIC is known. This thesis' purpose is to implement such a hardware that is suitable for low resource requirements. The focus within this is to optimize the algorithmic and to evaluate the trade off between area and execution time. The Ed25519 signature operations require the Secure-Hash-Algorightm-512 (SHA-512) hash function but this is not considered to be a crucial part and was therefore not included in the implementation.

The signature and verification process are not implemented because this functionality is straightforward and can be easily appended with a SHA-512 module. Therefore the implementation includes all necessary modules and functionality to perform the most important arithmetic ranging from the integer level up to scalar multiplication.

#### 1.1 Outline

In this thesis a historical view, an overview and a general discussion about cryptography will be provided in Chapter 1. Further, symmetric key cryptography will be touched and public key cryptography concepts will be presented.

In Chapter 3, the EdDSA signature algorithm will be discussed. This includes the general requirements, parameters and the algorithms necessary. Then the suggested explicit cryptographic scheme Ed25519 will be discussed and the necessary abstractions and the realization of the presented functionality will be outlined in detail.

The hardware implementation will be presented in Chapter 4. This consists of the used design flow and consideration of a hardware implementation in general. Subsequent to this, the implementation will be presented, starting from a high point of view down to the details. The chapter will end with the discussion about how the implementation was verified for correct calculations.

In chapter 5, the implementation's key facts will be presented and the evaluation of the best configuration will be made. The configurations considered best will then be compared to previous works regarding the key facts.

The conclusion will be presented in Chapter 6 which will end with suggestions of future work.

### Chapter 2

## Introduction to Cryptography

Cryptography comes into play when secrecy is involved. Secrecy has a long history and so does cryptography. In this chapter we will take a short look at its history. Afterwards, fundamental principles will be discussed and a higher-level view on symmetric-key cryptography and its counterpart public-key cryptography will be provided. Even though symmetric-key cryptography will be discussed, the focus will be on public-key cryptography, where elliptic-curve cryptography and signature systems will be dealt with in more detail.

**History and Basic Ideas** Cryptography has a long history. Even though he was not the first in history, Julius Caesar is known to have encrypted messages sent to his troops. Gaius Julius Caesar lived in the first century BC and therefore gives an idea about the long history of cryptography. As Simon Singh wrote in [36, Page 14], Caesar used various substitution ciphers. While he was fighting in Gaul, he used the substitution of replacing Roman letters with Greek ones. Further, the substitution of replacing letters with those that are three places further down the alphabet is called the Caesar Cipher. This mentioned cryptographic substitution and other methods until the 20th century were reversible on paper with a pen. In the 20th century a mentionable evolution took place by inventing cryptographic machines. A popular example for these was the Enigma machine, which can be categorized as electro-mechanical rotor cipher machine. It was used in World War II by the Germans. Simon Singh in [36, Page 149] also says that breaking the encryption of the Enigma machine shortened the duration of the war as the secret messages could be read by the Allied. The biggest step in the evolution of cryptography may be the invention of electronics performing cryptographic methods. Since then, reversing the encryption with paper and a pen by "hand" got practically infeasible.

A cryptographic method takes some input and by mapping, or some other mathematical relation, it generates output that is not recognized as the input. For a good cryptographic method, measurements and analysis give no clue about what the actual input was. These measurements might be statistical, counting the occurrences of single letters and groups of letters, mathematical calculations, or simple observations that can be made. In the context of statistical measurements, Shannon 1949 defined in [34, Pages 708-710] diffusion and confusion. He stated that **confusion** is the relation between the simple statistics of the output of a cryptographic method (ciphertext) and the simple description of the used key<sup>1</sup>. This relation should be as complex as possible. In other

$<sup>^{1}\</sup>mathrm{The}$  key can be seen as the secret password.

words, each bit<sup>2</sup> of the ciphertext should be as complex as possible related to as many bits of the key as possible. This has the effect that an attacker is prevented to use simple analysis to obtain the secret. **Diffusion** in his definition is the relation of the statistical structure of the message and the output of the cryptographic method. This can be illustrated, for instance, with the redundancy due to the occurrence of long combinations of letters. Analysis of representative texts in a specific language give probabilities of single words' occurrences. This occurrences can be used when the ciphertext is analyzed. But a cryptographic method with good diffusion generates output for which analysis results in useless information. In a wider interpretation, a good diffusion means changing a minimum amount of input leads to a significantly bigger change of the output.

By looking at the history, we can see the evolution from cryptographic scheme relying on keeping the scheme secret, to cryptographic schemes that are publicly available and rely on keeping the key secret. A cryptographic scheme that is not dependent on a secret key, and thus its security only relies on keeping the scheme secret, does not fulfill its purpose reliably. This relies on the simple circumstance that as more entities know the scheme, more possible targets are involved that can be attacked to get information about the scheme. Once the secret is gained by an attacker all others using the scheme are vulnerable. In contrast, a (publicly known) well engineered cryptographic scheme which depends on a secret key serves security more reliable. These cryptographic schemes further give the possibility to change the secret key if wanted and it is not required to engineer a new scheme from scratch.

Since their invention, computers, also have been utilized for cryptography. Therefore all the processed messages have digital representations. Following from this and the fact that computers in general are based on numbers, cryptography nowadays basically deals with mathematical problems. Concluding from the fact that the computation power of computers beat human capabilities by magnitudes, the related mathematical problems have to be hard to solve. Thus, cryptography is concerned with the design and analysis of methods that enable a secure communication in an insecure environment.

For a first look at cryptography, some aspects should be mentioned first. The terms entities, a sender, a receiver and an attacker, can relate to human beings, but not exclusively. As secrecy is a goal in all contexts that in any way deal with private data, an entity might also refer to a computer system, a web browser and its communication counterpart, a web server, or something similar. Further, a message is not required to be a human readable text. This may be a single data packet, when for example a web browser sends a request for a website or the login information, a wireless LAN adapter sends the password to the accesspoint, a car is unlocked via a remote control, or any other digitally generated sequence of symbols.

When thinking about cryptography and a scenario where cryptography is used, there are basically three entities involved. At a message-based view these are a sender, a receiver, and an entity which is not wanted by the sender and receiver to get or manipulate their messages. In literature, concerning cryptography, the two entities communicating are often called Alice and Bob. During an ongoing communication the role of sender and receiver might switch and can be either Alice or Bob. The third entity mentioned before is called Eve. She is assumed to have knowledge about the used cryptographic scheme, considerable computational resources and is able to read and modify all data that is sent over the communication channel. In the following, this convention also applies.

<sup>&</sup>lt;sup>2</sup>Any data or text that is stored in a computer can be broken into bits. A bit is the smallest unit used in computers and has two states, either one or zero.

Cryptography does not imply confidentiality in every case. As stated in [19, Section 1.1], the list below defines basic goals for schemes, this list, however here is not complete:

- Confidentiality: The information transferred between Alice and Bob is not readable for Eye.

- Data integrity: Bob can verify that the transferred message received from Alice has not been modified.

- Authentication: Bob can verify that the received message has indeed been written by Alice. Eve, in turn, can not create a message that is falsely accepted to have been written by Alice or Bob.

- Non-repudiation: A third neutral entity can verify that the very origin of the message created by Alice has indeed been Alice. Thus Alice cannot deny that she created it.

Depending on its purpose, a cryptographic scheme may combine the desired goals or may fulfill other goals such as anonymity for their communication entities or access control for restricting certain resources to specific entities. As an example for a scheme with certain purpose, with outlook on this thesis' topic, downloading a web browser's installation files does not have to be confidential. Nevertheless for security reasons it is desired to verify the origin to avoid installing a Trojan horse or some other type of virus. Here, authentication comes into play as one can verify if the downloaded files have been originated by the trusted developers who signed it.

#### 2.1 Symmetric-key Cryptography

For the following section and subsections, we refer to the *Introduction and Overview* section in [19, Section 1.1]. Symmetric-key cryptography relies on the idea that Alice and Bob share a common secret. This secret enables them to use methods that are publicly available. These public availability however does not harm security as the security is based on a hard to solve mathematical problem and the shared, but secret key. After agreeing on the shared secret, Alice uses the related cryptographic method with this key and the message as input. Afterwards she sends the obtained result to Bob. He uses the counterpart method and the shared key to reverse or verify the operation of Alice.

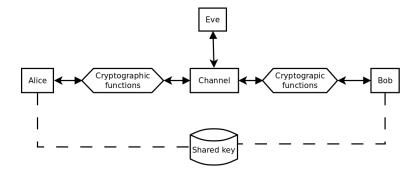

Figure 2.1 shows the basic scenario for symmetric-key cryptography.

Figure 2.1: Communication in an insecure environment

Depending on the cryptographic goal, the scheme is engineered to fulfill, the above described methods can vary: for example one of the operations can be encryption and the other the counterpart-operation decryption, or signature generation and signature verification. A popular cryptographic scheme based on symmetric-key cryptography is, for instance, the Advanced Encryption Standard(AES) that serve methods for encryption and decryption.

To give a little insight into methods of cryptography, the basic procedures to achieve cryptographic goals will be discussed on a high-level view for two exemplary goals. This will be done respecting the structure of symmetric-key cryptography. For the following description, the shared secret key is assumed to be already accessible. Thus, it must be generated and distributed prior to the actual communication. As the generation procedure is scheme-specific, it will not be discussed in detail. The key distribution, on the other hand, will be discussed in the following paragraph, which focuses on key distribution and management, because this is a significant disadvantage.

Confidentiality As described in short beforehand, confidentiality is achieved by an encryption- and decryption-method. The whole procedure of encryption and decryption with all its details is publicly available. This does not threaten the security since only the knowledge of the key delivers the right results, it merely simplifies the overall process of establishing a secure channel as only the key has to be shared in a secure way.

When using a encryption method, its output should differ if only a single bit within the input changes. This input refers to the message as well as the used key, what has been discussed in the first paragraph of this chapter, regarding confusion and diffusion. The differing bits of the original output compared to the one obtained with the one-bit-flipped-input should ideally be distributed over the whole range of output bits and flipping a certain bit should not be traceable to specific output bits.

Alice uses the encryption method with the shared key and the message as input to obtain the so called ciphertext. This ciphertext is sent over the insecure channel to Bob. After receiving the message he uses the decryption method with the same shared key as used by Alice and the ciphertext as input to obtain the original message. As already mentioned, Eve is able to read the ciphertext. But due to the lack of knowledge of the used key, she will not be able to compute the original message.

**Data integrity** If data integrity is desired the cryptographic scheme changes in some points compared to confidentiality. After Alice and Bob agreed on a shared key, Alice and Bob use a message authentication code (MAC) algorithm. Alice computes the authentication tag t using the MAC with the shared key and the message as input. The authentication tag is then sent along with the message to Bob. As Bob uses the same MAC algorithm, knows the shared key and received the message, he can compute the authentication tag t' on his own. He uses the message and the shared key as input for the MAC for computing t' and verify if t = t'. If the verification succeeds Bob knows that the message is indeed signed with the right shared key and that it is highly probable it was not modified by Eve and indeed sent by Alice.

#### 2.1.1 Key Distribution and Management

Symmetric key cryptography is based on the idea that two entities share a common key. This aspect leads to disadvantages regarding key distributing and key management, which will be discussed in the following paragraphs. The first discusses the problem of key distribution concerning the need of two entities participating a communication to agree on keying material. The second addresses the problem of managing the keying material in a system that is not limited locally.

#### 2.1.1.1 Key Distribution

Due to the principle of symmetric-key cryptography, the secret key has to be shared between both entities of communication. Sharing the keying material over an insecure channel assuming no one else reads it should not be the basis of a cryptographic system. This would harm the security from the very beginning. The shared key needs to be agreed on in a secure way. This can be assured by physically meeting or a secured channel. Meeting in person is not convenient as soon as the entities involved are spatial separated. The second possibility mentioned could be realized by a trusted courier or an already secured channel to a central distributing facility. Using a trusted courier gets impracticable with increasing distance between the entities. Further, in a scenario with two entities wanting to communicate over a global network such as the Internet, waiting days for the courier to arrive seems far from good. In a closed environment or a locally limited network each entity can initially agree on a key with the central key distributer. Entities then use the secure channel to the distributer to further agree and share keying material when required. But again, in applications concerning the Internet and global communication this is impracticable. For the initial agreeing on the keying material, each entity would have to either physically visit this facility, use a trusted courier or use an already established secure channel. As illustrated before, the first two possibilities have significant drawbacks. Let us assume, for now, that the central key distributer has local branches. For a practicable global system those branches with appropriate keying material would have to be spread all over the world. Further, each of these entities would have to be trusted and secured to ensure no leaking of keying material. This would end up in a huge organization that might never get efficient and convenient for users. Another aspect of the central distributing facility is the growing amount of necessary distribution in operating state. With the large number of nodes participating in the Internet in mind, including not only the server but each computer and mobile device, and assuming each node has separated and secured applications, each needing a secret key, the resulting amount of distribution cannot be handled by a central facility.

#### 2.1.1.2 Key Management

With the increasing number of communication partners, another disadvantage arises. For each of the communication partners, an entity has to store a shared key. This gets impracticable or impossible in applications with limited storage space. This problem can again be handled by a central facility with an initially shared key and thus secured channel. The keys can be managed by the central facility and on demand obtained over the secured channel. As in the previous paragraph, this is impracticable as soon as the number of entities reach just a fraction of the number of nodes in the Internet. Then the management efforts evolve to a serious problem.

Another problem can be imagined in a scenario with a central key management facility. The keying material is shared between at least three entities, both of the end-point entities and the facility. Therefore, this limits the achievable goals of a scheme as non-repudiation is not possible, as [19, Section 1.1] clarifies.

#### 2.2 Public-key Cryptography

Diffie, Hellman and Merkle 1976 in [12] published the concept of a public-key cryptography scheme to handle the disadvantages regarding the key distribution. The concept was engineered to enable security over an insecure channel without the requirement to share a secret previously. Still, the requirement to distribute the public key of an entity in an authentic way has to be met. In contrast to symmetric-key cryptography, this concept is not based on the fact that both entities of the communication share the same key, but each entity has two keys: One for the encryption of messages destined to it, and one for the decryption of messages it received. Due to this, public-key cryptography is also called asymmetric-key cryptography.

The underlying idea is to use a one-way function. This means, given the result of such a function, it is not possible or computational infeasible to reverse the operation without special knowledge. Here, the pair of keys come into play. In the concept, the public key and the message are used as input of the one-way function. Only the knowledge of the private key enables the back transformation to obtain the original message. This requires the public as well as the secret key to be related in a special mathematical way.

Whereas the concept of Diffie, Hellman and Merkle was the first publicly published, a public-key cryptographic system was engineered by Great Britain's Government Communications Headquarters starting at 1969 until 1975, but this was kept secret as Simon Singh in [36, Chapter 5, Page 211] stated. As Simon Singh writes further, Diffie, Hellman and Merkle discovered the concept of public-key cryptography and the need of one-way functions but failed to be the first to publish a working system as they failed to find such a function. But inspired by their concept, this race was won by Rivest, Shamir and Adleman. They found such a one-way function and proposed it 1978. In Subsection 2.2.4 it is discussed and for more detail see the article of Rivest, Shamir and Adleman [30].

After Rivest, Shamir and Adleman's scheme, other public-key cryptography schemes based on different hard to solve mathematical problems were introduced in the following years. Popular mathematical hard problems, in context of cryptography, will be discussed in the following sections.

#### 2.2.1 Concept of Public-key Cryptography

An entity has two keys related to it: the private key and the public key. The private key, as the name already suggests, is kept secret and the public key is distributed to the communication partners in an authentic way. The public and the private key are generated as a pair with a certain mathematical relation. The generation of the keys is computationally easy whereas the reverse computation of the private key with only knowing the public key is computationally extremely difficult. The mentioned mathematical relation results in the following circumstance: The result of a cryptographic method cannot be reversed without knowledge of the counterpart key or the computational effort is higher than trying all possible keys. Therefore, by the use of appropriate long keys, significant security can be assured. This circumstance is referred to as one-way function.

#### 2.2.2 Exemplary Goals

As the central element, the used keys of the cryptographic system changes in contrast to symmetric-key cryptography. The procedures to achieve cryptographic goals are exemplary discussed in the following.

Confidentiality The discussion about achieving confidentiality in public-key cryptography, in contrast to symmetric-key cryptography, starts with obtaining the keys. To encrypt a message destined to Alice, Bob obtains an authentic copy of Alice's public key. He computes the ciphertext with Alice's public key and the message as input for the encrypt method, and sends it to Alice. Alice computes the original message with her private key and the ciphertext as input for the decryption method.

**Authentication** Authentication is used to either check the authenticity of signed data or an entity.

In general, verifying an entity can be accomplished by a some sort of secret password or by a system of sending a challenge and checking the response. There, the response can only be computed with knowledge of the secret key.

Authentication of data serves the ability to reliably verify that the data was indeed sent by the entity. In turn, this also ensures that the data was not modified as different data causes a different signature. To be able to do this, an entity needs a unique attribute. In public-key cryptography this unique characteristic is directly served by each entities' keys. When Alice wants to write a message to Bob and wants to guarantee him the ability to verify that she indeed wrote it, she signs it. She uses her private key and the message as input for the signature generation function to create a digital signature and sends the signature, along with the message, to Bob. He can verify that the message was written by Alice with her public key. Therefore he checks if the received signature was created by Alice. He further checks if the signature was created for the received message. The verification is only then successful, when both checks succeeded. For public-key cryptography schemes it is characteristic that only the possessor of the private key can create a digital signature which passes the verification method. The signature generation procedure generates different signatures for each message and thus a signature generated for a certain message is only valid for this message.

#### 2.2.3 Mathematical Hard Problems

The mathematical problems which are used in cryptographic schemes have in common that an easy calculated result of the related operation cannot be easily reversed to obtain the original inputs. Such an operation is called one-way function. The mathematical problems differ in the necessary effort to reverse the cryptographic function. This necessary effort is here referred to as hardness. The hardness measurement is based on the best known algorithm to solve the problem. Thus, a new algorithm to solve a particular mathematical problem might lower the attributed hardness.

The most notable mathematical hard problems, due to their use in cryptographic schemes, are the integer factorization problem and the discrete logarithm problem. Based on the discrete logarithm problem, the elliptic curve discrete logarithm problem was developed.

#### 2.2.4 The RSA Cryptographic Scheme

The RSA is a cryptographic scheme published 1978 by Rivest, Shamir and Adleman. For detailed description and further information not covered here see their article [30]. In this section, for simplification the word integer refers to a positive integer.

It was the first public-key cryptography scheme after the concept was published by Diffie, Hellman and Merkle. 30 years after its publication, RSA is still widely used. The

hardness of the integer factorization problem forms the base for the hardness of breaking the RSA. To give an impression of one-way functions and mathematical hard problems, the principle of the integer factorization problem will be discussed here. Further the factorization of an 232 digits long integer will be discussed to get an idea of the necessary effort to reverse a one-way function.

Calculating the result of an integer multiplication is rather simple. Even for rather big numbers with several hundreds of bits, the result can be obtained in fractions of a second as soon as a computer is involved. In contrast to this, the reverse operation, namely the factorization, of a commonly big integer on a single computer takes hundreds of years as discussed in the following.

Integer factorization is the operation to reverse a multiplication and thus to find the multiplicands used. The fundamental theorem of arithmetic, see the reprint of Gauss' Disquisitiones Arithmeticae [18], states that the factorization of an integer is unique. Thus, once the factorization is completed, this is the only factorization possible. To check if a number  $B_1$  is a factor of the integer  $A_0$ , the division  $A_0/B_1 = A_1$  has to be carried out. If the devision has no remainder,  $B_1$  is a factor. If  $B_1$  is a prime,  $B_1$  does not have to be factorized itself, as primes are only divided by 1 and the prime itself with no remainder. Basically, integer factors cannot be greater than the product. Thus, a strategy to find a factor of a number might be to divide by all these numbers until it delivers no remainder. A division by 1 can be carried out infinitely often with no remainder and serving no practical information about the factors. The division by the number itself does not have a remainder too, the result is 1 and also results in no information about the factors. These divisions are omitted. Further limitations to the factors that are tested can be made: Only numbers up to the square root of the product must be checked as bigger numbers would already be the result of the division by a smaller number than the square root. Every time a factor  $B_i$  is found, the search is restarted, but with the result  $A_i$  of the division  $A_{i-1}/B_i = A_i$  as number to be factorized. Repeating this procedure until all factors are primes delivers the factorization of an integer number. That might not evolve a problem and can be calculated on paper as long as the number to factorize is small enough. Imagine to factorize an integer being the product of primes having hundreds of digits and are of similar length. Although more efficient algorithms than the trivial trying of all possibilities exist, until now, the integer factorization problem has no solution which would harm cryptographic schemes based on it using appropriate big integers. The factorization of the integer described in the following was done using such a more efficient algorithm.

In the cryptoeprint report [24] the factorization of a 768-bit number was reported in 2010. Specifically this number, called RSA-768, has no special structure that may give the possibility to accelerate the computation. Therefore it is categorized as the factorization of a general integer and the best known algorithm was used. The stated computational effort spent would take almost 2000 years if it was run on a single core 2.2 GHz AMD Opteron processor with 2 GB Random Access Memory (RAM). The actual time spent to obtain the factorization on the specialized hardware was two years. In contrast to this, the effort to compute the RSA-768 integer by multiplication of its factors is about 0.26 microseconds due to a rough estimation. Thus, the hardness of the integer factorization is obvious. For information and details of the number-field sieve-factoring method see the book of Lenstra and Lenstra [27] as this is not discussed here.

The above mentioned estimation with its assumptions is described in the following: The RSA-768 integer is a 768-bit integer with 232 decimal digits. Its factors are reported as two 384-bit integers. For the multiplication, the product scanning form is assumed as the factors are too wide for commonly used multiplication units in processors. For details of product scanning multiplication see [19, Subsection 2.2.2, Page 32]. Due to this  $n^2$ multiplications of b-bit integer words are needed where n is the number of words the integer is split into. Each multiplication is assumed to take one cycle whereas for the fetching of the operands, the storing of the results and the accumulation after the multiplication, three cycles are added per multiplication. The chosen word width of the multiplication unit is 64 bits because the AMD Opteron has 64-bit multiplication capabilities, as stated in the data sheet [1]. Therefore the 384-bit integers are split into 12 words which leads to n=12 and further  $12^2 \cdot 4 = 576$  cycles are estimated. On a 2.2 GHz processor with assumed  $2.2 \cdot 10^9$  instructions per second, the whole multiplication will take about 0.26 microseconds. A strong emphasis lies on the fact that this is a rough estimation and the real execution time of the multiplication depends on the possible optimization and the necessary overhead due to the architecture. As this estimation is thought to illustrate the contrast between computing the result of an one-way function and reversing it, this rough estimation is considered sufficient.

#### 2.2.5 Elliptic Curve Discrete Logarithm Problem

The elliptic curve discrete logarithm problem is based on the discrete logarithm, more precisely it is the discrete logarithm with the group of points on elliptic curves over a finite field. As Hankerson, Menezes and Vanstone write in [19, Chapter 1, Page 1], the use of elliptic curves in cryptography was suggested independently by Neal Koblitz [25] and Victor Miller [28]. In the following paragraphs, the basic mathematical relations are discussed, starting with groups, continued with finite fields and the discrete logarithm. Here, elliptic curves over finite fields are developed starting from a geometric point of view. Afterwards the base is built for the discussion about elliptic curve discrete logarithm problem. Finally, curve types and coordinate systems are discussed in short. The mathematics discussed here can be read in Guide to Elliptic Curve Cryptography of Hankerson, Menezes and Vanstone [19, Subsections 1.2.3 and Section 2.1], Combinatorial group theory of Karrass, Magnus and Solitar [23, Section 1.1] and Elliptic Curves: Number Theory and Cryptography of Lawrence Washington [40] for further details and explanations, and more specific references will provided alongside the discussion.

#### 2.2.5.1 Groups And Finite Fields

The term group here is meant in a mathematical sense: A group is defined as a set of elements and an operation that can be carried out. For the group  $(G, \cdot)$ , G is the set of elements and  $\cdot$  is the binary operation. Groups and their properties will be discussed in the following as in [23, Section 1.1]. A group  $(G, \cdot)$  is called finite if the number of elements in the set G is finite. The binary operation takes two elements of the set. Since  $(G, \cdot)$  is a group, the following four properties are satisfied:

- I Given an ordered pair a, b of elements of the set G, a third element c is uniquely determined by  $a \cdot b = c$ . This is often written as ab = c where the operation's sign is omitted.

- **II** The binary operation  $\cdot$  of the group  $(G, \cdot)$  is associative:  $(a \cdot b) \cdot c = a \cdot (b \cdot c)$ .

- **III** In the set G an element  $e \in G$  exists, such that  $e \cdot a = a \cdot e = a$  for all  $a \in G$ . e is called the *identity* or *unit* and is also written as 1.

- **IV** In the set G, for each  $a \in G$  an element  $b \in G$  exists, such that  $a \cdot b = b \cdot a = 1$ . This element is called the inverse<sup>3</sup>.

If the following fifth property is satisfied, the group is commutative and is called an abelian group.

**V** For each  $a, b \in G$  of  $(G, \cdot)$ ,  $a \cdot b = b \cdot a$  is true.

Suppose we have a finite multiplicative group  $(G,\cdot)$  of order q, which means the set of the group has q elements. [19, Page 12] states for an element  $g \in G$  a smallest integer t exists, such that  $g^t = 1$ . Then it is said that t is the order of g. It is stated that for every element  $g \in G$  such a t exist. The element  $g \in G$  form a cyclic subgroup of  $(G,\cdot)$  with the powers of g as the elements of the set and the same binary operation as G. The elements of the group are written as  $\langle g \rangle = \{g^0, g^1, ..., g^{t-1}\}$  and the group  $(\langle g \rangle, \cdot)$  is called a cyclic subgroup of G generated by g. The same applies to finite additive groups, but then gt = 0, which means adding t copies of g, and  $\langle g \rangle$  is the set of multiples of g. If an element  $g \in G$  exists, such that the order of the element is equal to the order of the group, the element is called a generator of G.

Groups are a part of the abstract algebra and might seem to be a theoretical construct with no benefit. But the integer mathematics can be expressed in groups. In context of the logarithm, the multiplicative group of integers can be replaced by another multiplicative group. If this group is chosen appropriately it results in increased hardness of computing the result of logarithm. Before discussing this in more detail, some more necessary mathematics will be discussed to complete the base of the elliptic curve discrete logarithm problem.

To describe the elliptic curve discrete logarithm problem it is necessary to discuss finite fields. A finite field over the prime p is the triple  $(\mathbb{F}_p, +, \cdot)$  with a finite number of elements as discussed in [40, Page 482]. The elements of the set  $\mathbb{F}_p$  are the positive integers modulo p:  $\mathbb{F}_p = \{0, 1, ..., p-1\}$ . A finite field has two operations, with symbols + and  $\cdot$ , called addition and multiplication. With each of these operations a group is defined and will be discussed in the following:

As discussed in [19, Subsection 1.2.3], the addition operation + together with the set  $\mathbb{F}_p$  form the additive group  $(\mathbb{F}_p, +)$  which is an abelian group. Thus  $a, b, c \in \mathbb{F}_p : a + b = c$  and c is the result of the integer addition modulo p: c = a + b modulo p. Further, 0 is the identity and -a is the inverse of  $a \in \mathbb{F}_p$ . Thus, given  $a \in \mathbb{F}_p$ , a + 0 = a, and a + (-a) = 0. The multiplication operation with all nonzero elements  $\mathbb{F}_p^*$  of the same set form a multiplicative group  $(\mathbb{F}_p^*, \cdot)$ . Just as the additive group, the multiplicative is abelian too. Here  $\mathbb{F}_p^*$  is used instead of  $\mathbb{F}_p$  as there is no inverse for zero and  $\mathbb{F}_p^*$  is the set of positive, nonzero integers modulo p,  $\mathbb{F}_p^* = \mathbb{F}_p \setminus \{0\}$ . The binary operation is the integer multiplication modulo p:  $a, b, c \in \mathbb{F}_p^*$ :  $a \cdot b = c$  and thus the result is calculated as  $c = a \cdot b$  modulo p. In this group the identity is 1 and the inverse of  $a \in \mathbb{F}_p^*$  is written as  $a^{-1}$ : given an  $a \in \mathbb{F}_p^*$ ,  $a \cdot 1 = a$  and  $a \cdot a^{-1} = 1$ .

Some more properties apply to finite fields and are listed in the following list. The interested reader might read [19, Section 2.1] for a detailed discussion.

<sup>&</sup>lt;sup>3</sup>If the group( $G, \cdot$ ) is an multiplicative group the inverse of a is written as  $a^{-1}$ , in case of an additive group it is written as -a.

- For a finite field it is required that the identity elements of the additive and multiplicative group are distinct.

- The multiplication distributes over the addition: Given  $(\mathbb{F}_p, +, \cdot)$  then  $a, b, c \in \mathbb{F}_p$ :  $(a+b) \cdot c = a \cdot c + b \cdot c$ .

- For each prime p a finite field  $(\mathbb{F}_p, +, \cdot)$  exists.

- The addition of an additive inverse might also be written without the addition sign: Given  $(\mathbb{F}_p, +, \cdot)$  and  $a, b \in \mathbb{F}_p$ , then a + (-b) might be written as a b and referred to as subtraction.

- Similar to addition, the multiplication with the multiplicative inverse  $a \cdot b^{-1}$  might be written as a/b and referred to as division.

Beside the mathematical definitions and properties, addition, multiplication and their counterpart operations in finite fields behave like ordinary integer with a subsequent modulo operation on the result.

#### 2.2.5.2 The Discrete Logarithm Problem

The name elliptic curve discrete logarithm problem already indicates its relation to discrete logarithm. But before discussing directly the elliptic curve discrete logarithm problem itself, the discrete logarithm problem will be discussed here in a basic manner. The discrete logarithm is similar to the ordinary logarithm, the solution for x in the equation  $a^x = b$ , but in contrast operates on a finite cyclic group. The group is assumed to be written as multiplicative group. A discussion about discrete logarithm can be read in [40, Chapter 5] and [19, Section 1.2] for discussion about discrete logarithm systems.

The fact that the discrete logarithm operates on finite cyclic groups leads to some advantage over the ordinary logarithm in the context of computational hardness: The ordinary logarithm allows using the already calculated powers of a to make bigger "jumps". For instance while testing the first 20 powers of a, these are saved. After this, the previous result  $a^i$  is not multiplied by a but  $a^{20}$  and then tested whether b is still bigger. If this is the case, the time doing 19 multiplications was saved. If not,  $a^i$  can be multiplied with  $a^{10}$ and tested again, which gives a direct hint if either x is between i and i + 10 or between i+10 and i+20. In contrast to this, the finite cyclic group prohibits this shortcut. Take the group of positive integers less than 17 with the group operation defined as the integer multiplication modulo 17, ( $\{0,1,...,16\}$ , ·). Here  $4^2 = 4 \cdot 4 = 16$  whereas  $4^3 = 13$  as  $64 \mod 17 = 13$ . As in the general case, observing the results of the group operations does not give a clue of how many operations are sill necessary. The alternative strategy left is to calculate the powers of  $a:a^i$  with increasing i and comparing the result with b. This is done by calculating the group operation  $a^{i-1} \cdot a = a^i$  starting with  $a^1 = a$ . Thus, this requires x-1 group operations. Therefore, beside the value of x, the hardness of the discrete logarithm problem depends on the used group and the complexity of its operation.

#### 2.2.5.3 Elliptic Curves Over Finite Fields

In this section some aspects of elliptic curves will be discussed. Elliptic curves will be developed from a geometric view of elliptic curves, to a group law and end with elliptic curves defined over finite fields. The discussion in this section refers to Washington's

Elliptic Curves: Number Theory and Cryptography [40] and detailed reference will be provided in the text.

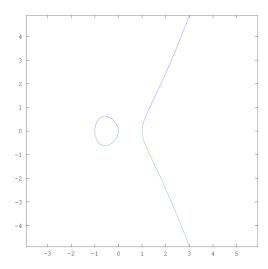

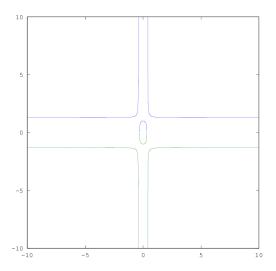

In the context of visualization of elliptic curves, we assume these are defined over real numbers. By doing so, we get more intuitive visualizations. Elliptic curves are plane curves as an elliptic curve in affine coordinates has two coordinates. The name might let one think of shapes with an elliptic form, but it is derived from a mathematical relation. Silverman in [35, Chapter VI, Page 157] writes therefore that elliptic curves " ... are the Riemann surfaces associated to the arc-length integrals of ellipses". Elliptic curves do not look like ellipses in general as shown in Figures 2.2 and 2.3.

Figure 2.2: Curve  $y^2 = x^3 - x$

Figure 2.3: Curve  $y^2 = x^3 - x + 1$

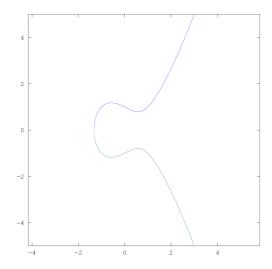

Points on it have affine<sup>4</sup> coordinates, x and y, and satisfy the Weierstrass equation<sup>5</sup>  $y^2 = x^3 + ax + b$ , where x and y are the x coordinate and respectively the y coordinate, a and b are constants determined by the used elliptic curve. Further for the elements x, y, a, b in the equation, it has to be specified to which set they belong. As a, b are specified to be elements of the set of a field K, the elliptic curve is said to be an elliptic curve over K. x, y specify the coordinates of a point on the elliptic curve and are of the set of the field L, with  $L \supseteq K$ . For technical reasons the point at infinity is included in L:  $\infty \in L$ . This has advantages when a third point is calculated out of two known points: Due to Bezout's theorem an elliptic curve intersects with a line at exactly three points. For fully respecting this theorem some special cases have to be discussed. The intersections can be one of four types and are visualized in Figure 2.4.

The general case, when the line is neither vertical nor a tangent to the curve, is shown by the blue line in Figure 2.4. As long as none of the two points is a tangent and the resulting line is not vertical, the angle and the position of the line has no restrictions. Then it intersects the curve at 3 points.

If the line is geometrically a vertical line, the intersection is defined to be at infinity, see the magenta and the red line in Figure 2.4. For details about the intersection at infinity see [40, Sections 2.1, 2.2 and 2.3].

If the line is a tangent to the curve, see the green and magenta line in Figure 2.4, the point is counted twice and the line intersects the curve at exactly one more point, either at infinity (magenta) or "normal" (green).

Figure 2.4: Curve  $y^2 = x^3 - x + 1$  with 4 different intersections

As a consequence of the  $y^2$  in the equation, an elliptic curve is symmetric to the x axis: By the basic rules of mathematics, for calculating y out of  $y^2$ , it must be written as  $y = \pm \sqrt{y^2} = \pm \sqrt{x^3 + A \cdot x + B}$ . The negative of a point  $P_1 = (x_1, y_1)$  is defined to be  $-P_1 = (x_1, -y_1)$ .

<sup>&</sup>lt;sup>4</sup>The representation of points can done in other coordinate systems. This is discussed in Subsection 2.2.5.6.

<sup>&</sup>lt;sup>5</sup>This is the Weierstrass equation for elliptic curves which do not have a characteristic of 2 or 3. A more general equation and discussion for those two cases can be found in [40, Equation 2.1, Page 10].

By examining the intersection with a line we can define a point-addition operation on elliptic curves,  $P_1 + P_2 = -P_3$  or  $P_1 + P_2 + P_3 = 0$ .

- 1. **General case:** A line through two points,  $P_1 = (x_1, y_1)$  and  $P_2 = (x_2, y_2)$ , on the curve, intersects the curve at one more point if none of the points is a tangent and the line is not vertical. The line has a slope  $s = \frac{y_2 y_1}{x_2 x_1}$  and the third point  $P_3 = (x_3, y_3)$  can be calculated with  $x_3 = s^2 x_1 x_2$  and  $-y_3 = s \cdot (x_3 x_1) + y_1$ . The mathematical background for this is to find the third root of the equation. This is eased by the knowledge of the other two roots. Details of the mathematics can be found in [40, Section 2.2].

- 2. **Tangent:** If two points on a curve are very close together, a line through them converge to a tangent of the curve. As a consequence here, if the point is added to itself, the line is a tangent of the curve at this point. The tangent is the first derivation of the equation at this point. Here it is assumed that the line is not vertical. Again, the line intersects the curve at exactly one other point. By implicit differentiation of  $\frac{d}{dx}((y)^2) = \frac{d}{dx}(x^3 + A \cdot x + B)$  one gets  $2y \cdot \frac{dy}{dx} = 3x^2 + A$  and  $\frac{dy}{dx} = \frac{3x^2 + A}{2y}$ . As the x, y coordinate of this point is available, the slope s of the line is  $s = \frac{dy}{dx} = \frac{3x_1^2 + A}{2y_1}$ . When proceeding as in the previous case, but with  $P_1 = P_2$ , we get  $x_3 = s^2 2x_1$  and  $-y_3 = s(x_3 x_1) + y_1$ .

- 3. Vertical case: If the x coordinates  $x_1, x_2$  are equal, the line through the two points is a vertical line. Here the y coordinates  $y_1, y_2$  are not equal. As mentioned before,  $\infty$  is added to the points on the curve and is said to sit on the top of the y axis. If then a line connecting two points is vertical, the line intersects the curve at  $\infty$ ,  $P_3 = \infty$ . By the circumstance that an elliptic curve is symmetric with respect to the x axis,  $y_2 = -y_1$ , thus  $P_2 = -P_1$  and  $P_1 P_1 = \infty$

- 4. Vertical tangent: This is case 2 and 3 combined,  $x_1 = x_2$  and  $y_1 = y_2 = 0$ . First, the line is a tangent as both points have the same coordinates and second, this tangent is vertical as both points' x coordinate are equal. Since the line is a tangent, the point of the intersection is counted twice and as it is a vertical line, the third intersection point is at  $\infty$ ,  $P_3 = \infty$ .

Recapitulating the properties of a group as discussed in Subsection 2.2.5.1, the properties I, III and IV of a group and further the property V of an abelian group can be shown to be fulfilled by the point-addition operation with  $\infty$  as the identity element. Showing that property II, the associativity, is fulfilled is rather complicated and would exceed the introductive manner of this section. The interested reader might examine [40, Section 2.4, Pages 20-35], who proves associativity by examining the intersections of lines through three points and handling the different types of intersections of a line and an elliptic curve.

- I Two points on the curve can be added by use of the above discussed cases.

- III Adding the identity  $\infty$  to a point  $P_1$ ,  $P_1 + \infty = -P_3$ , results in  $P_3 = P_1$  and is directly obtained from the above discussed "Vertical case".

- IV As III, using the "Vertical case" and the circumstance that  $P_2 = -P_1$  is a valid point on the curve,  $P_1 P_1 = \infty$ .

V A line through two points remains the same line, regardless which of the points is the starting point and the end point, therefore  $P_1 + P_2 = P_2 + P_1 = P_3$  holds.

The points on an elliptic curve and the point addition operation form a group as defined before in Subsection 2.2.5.1. The operation is usually called "the addition of points on an elliptic curve". In the later part of this thesis, the multiplication of a point P with a scalar n, often referenced as scalar multiplication or point multiplication, will be done by adding n times the point P.

We discussed the intersection of a line through points on an elliptic curve over real numbers and developed the group structure of points on an elliptic curve with the point addition as its binary operation. We may now continue with elliptic curves over finite fields. A, B, x, y are now elements of this field. This means a point  $P_1 = (x_1, y_1)$  has the coordinates as elements of this finite field. Calculations are done within this field and remain valid although the group of real numbers is replaced by a finite field. One may think of layers for the calculation and caution is in some sense necessary, as the operations' signs are similar but do not mean the same operation:  $P_1+P_2$  stands for the point addition of the group of points on an elliptic curve. For calculation this means to proceed as defined beforehand, for instance in the general case, calculating  $s = \frac{y_2 - y_1}{x_2 - x_1}$ ,  $x_3 = s^2 - x_1 - x_2$  and  $-y_3 = s \cdot (x_3 - x_1) + y_1$ . The division, squaring, multiplication, subtraction and addition stated in the formulas of the point addition for  $s, x_3, y_3$  is meant to be done in the field over which the elliptic curve is defined. In case of finite field over  $\mathbb{F}_q$  a prime q, regarding s, this results in doing the numerator's finite-field subtraction, the finite-field inversion of the result of the denominator's finite-field subtraction and the finite-field multiplication of both intermediate results. This similarly applies to  $x_3$  and  $y_3$ . These finite-field operations, as discussed in Subsection 2.2.5.1, in turn consist of integer operations with additional modulo operations, for instance  $y_2 - y_1 = integer\_value(y_2) - integer\_value(y_1) \mod q$ . Note, that the "integer\_value" is included to distinguish between the elements of the finite field and integer numbers.

As [40, Chapter 4, Page 95] states, elliptic curves over finite fields have only a finite number of valid points, as the finite field only has a finite number of possible combinations for the coordinates x, y of a point P = (x, y). It is further stated, that the exact number of valid points is difficult to compute for big finite fields, but increases with the number of elements in the field.

Assuming a point P on an elliptic curve over a finite field  $E(\mathbb{F}_q)$  and  $\infty$  as the identity element. As discussed in Subsection 2.2.5.3, a t exists and t is the smallest integer such that  $t \cdot P = \infty$ . In this manner cyclic subgroups generated by elements of order q can be defined.

#### 2.2.5.4 The Discrete Logarithm With Elliptic Curves

After discussing the discrete logarithm in general and elliptic curves over finite fields, we continue with the discrete logarithm with a cyclic subgroup of the group with the set of points on an elliptic curve defined over a finite field over a prime. The name already indicates the involved mathematics. In the following, the necessary steps and the layers of computation are outlined and the main aspects are recapitulated in short to give a rough overview. For a more detailed discussion see the referred sections and the referenced sources.

To proceed top down, we start with the discrete logarithm. This is to find a solution for k in the equation  $a^k = b$ , with given a, b as we discussed in Subsection 2.2.5.2. As the

structure of computed data permits shortcuts, this is done by computing the powers of one after another and comparing these results with the specified result. The next topic is the group to which the elements a, b belong to, that leads to the cyclic subgroup of the group of points on an elliptic curve with the point addition as the group's binary operation and was discussed in the previous Subsection 2.2.5.3. In this group, copies of the generating point on the elliptic curve are summed up for calculating a multiple of a point, the scalar multiplication. As a consequence of the circumstance that the group operation is addition and not multiplication, the discrete logarithm here computes k out of  $a \cdot k = b$ . The scalar multiplication, see Subsection 2.2.5.3, in turn, stands for several finite-field operations, as previously stated in Subsection 2.2.5.1. These operations cover the basic usual mathematical operations, addition, subtraction, multiplication, inversion and negation, and are computed as their pendants in usual mathematics with a trailed modulo operation.

Regarding the scalar multiplication, the drafted summing up of copies of a specific point would results in a repeated point addition, therefore calculating kP would need k-1 point addition operations. That can be shortened by a "double and add". This procedure takes P as the initial value of the intermediate result R, starting with the most significant bit being 1 and testing each bit down to the least significant, R is doubled and, according to whether the bit is either set 1 or 0, either P is added to the intermediate or not. For instance we perform the scalar multiplication of a point with 19. The most significant bit set corresponds to  $2^4 = 16$ , therefore the bits for  $2^3 = 8$ ,  $2^2 = 4$ ,  $2^1 = 2$  and  $2^0 = 1$  are tested. For illustration the index of R will be increased for each bit tested, starting with  $R_0 = P$ . The first bit tested,  $2^3$ , is not set 1, so  $R_1 = 2 \cdot R_0$ . The same applies to  $2^2$ , so  $R_2 = 2 \cdot R_3$ . The bits for  $2^1$  and  $2^0$  are both 1, so the intermediate and afterwards the final result get  $R_3 = 2 \cdot R_2 + P$  and  $R_4 = 2 \cdot R_3 + P$ . Here, instead of 19 additions, the result is obtained after four doubles and two additions.

#### 2.2.5.5 Curve types

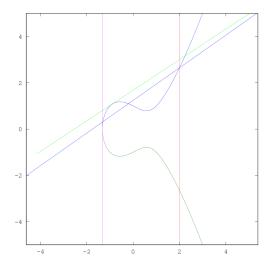

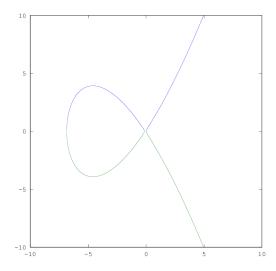

The family of elliptic curves is not limited to curves in Weierstrass form. Due to the introductive manner of this section, besides the already mentioned and analyzed Weierstrass curves, twisted Edwards curves will be discussed. As a central topic in this thesis, see the next Chapter 3 for further discussion on twisted Edwards curves.

Different types of curves are expressed by different equations defining such a curve. Those types differ in the way the point addition is done, as discussed in Subsection 2.2.5.3, its formulas are derived from the curve equation. Certain formulas for the point addition of a curve type can have benefits over other types regarding various disciplines. While one type can be the fastest in computation on certain specific architecture and a specific hardware, another type can have attack-resistance advantages over others.

As different types are still part of the family of elliptic curves, it may seem reasonable that some curves of one type may be convertible to other types. This is not true in general, but for instance, as Bernstein, Birkner, Joye, Lange and Peters stated in [11], for every Montgomery curve a twisted Edwards curve can be calculated. As a consequence, it is possible for curves to be converted into another type to take advantage of this type's properties. See Figure 2.5 for the visualization of a twisted Edwards curve and Figure 2.6 for a Montgomery curve. For using such a conversion, one converts the curve equation and the input point for the scalar multiplication. Then the result of the scalar multiplication can be calculated using the new curve's point-addition formulas and then finally the point

is converted back to the original curve.

Figure 2.5: Twisted Edwards curve  $10x^2 + y^2 = 1 + 6x^2y^2$

Figure 2.6: Montgomery curve  $3y^2 = x^3 + 10x^2 + x$

#### 2.2.5.6 Coordinate systems

As mentioned in Subsection 2.2.5.5, different types of curves can provide certain advantages. Similar to this, coordinate systems allow, for instance, to optimize the speed of calculation for a particular architecture or hardware. The chosen coordinate system also has an influence on the space requirements during calculation as different coordinate systems store additional values. The coordinate system has a direct impact on the point-addition